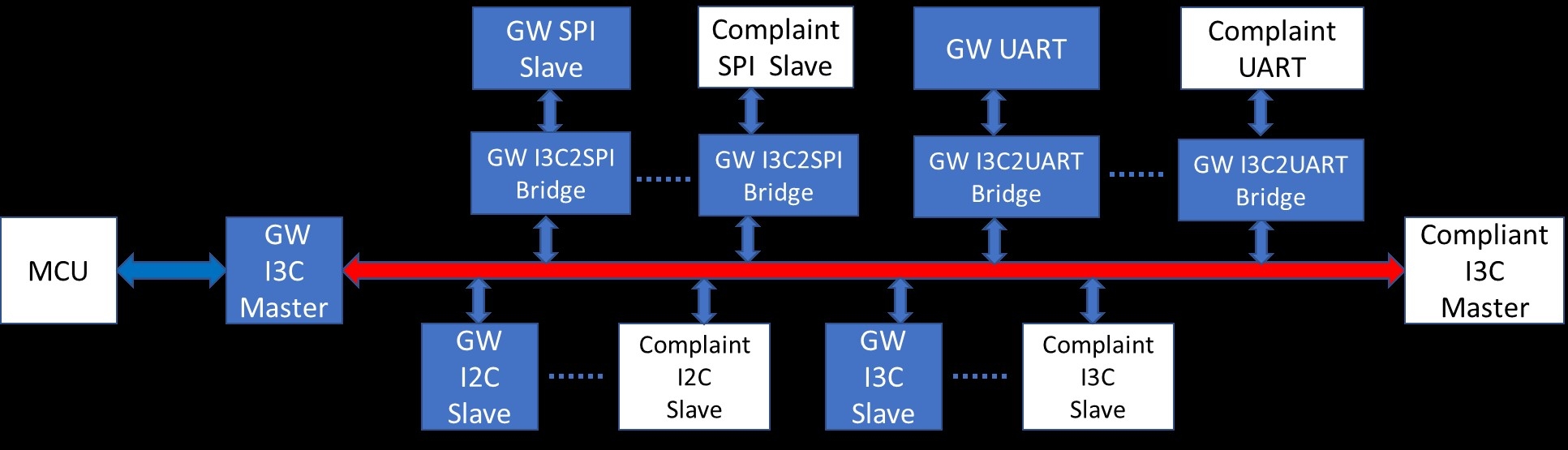

I3C is a new generation two-wire serial bus interface developed by MIPI Alliance Sensor Working Group and collaborated by industry-wide sensor chip makers, IP companies and Top-Tier ODMs in mobile and embedded markets. I3C is targeted to be a fundamental interface for mobile, embedded system and IoT applications; it is an extension of former I2C standard and downward compatible. GOWIN Semiconductor Corp, a member of MIPI Alliance, offers the GWI3C IP solution, which is fully compliant with MIPI Alliance’s I3C standard. The IP can be dynamically configured to be I3C Master or I3C Slave, implemented within GW1N family FPGA, for communicating seamlessly with any other devices compliant with MIPI Alliance SWG I3C and I2C standard.

I3C Typical Application

- Motion sensing (gyro, accelerometer)

- Environment perceptional sensing (sounds, light, temperature, humidity)

- Bionics sensing (fingerprint, heart rate monitoring, respiratory frequency)

- Communication (NFC, IrDA)

GWI3C Basic Features

- Feasible and programmable: support adjustable data and clock duty cycle in high precision, to achieve wide range data transmission rate,

- Support static addressing

- Support dynamic addressing

- Support I3C address arbitration

- Single Data Rate (SDR)

GWI3C Advanced Features

- Support hot-socket

- Support dynamic addressing in hot-socket

- Supports Slave requests Secondary Master (SDR-only)

- Support In-band Interrupts

- Support Common Command Code (CCC)

GW13C Transmission Rate

GOWIN YunYuanÒ EDA fully automates the GWI3C IP (Master-Slave-Combined) design integration with user application. GWI3C IP (SDR-mode) supports data rate up to 12.5Mbps.

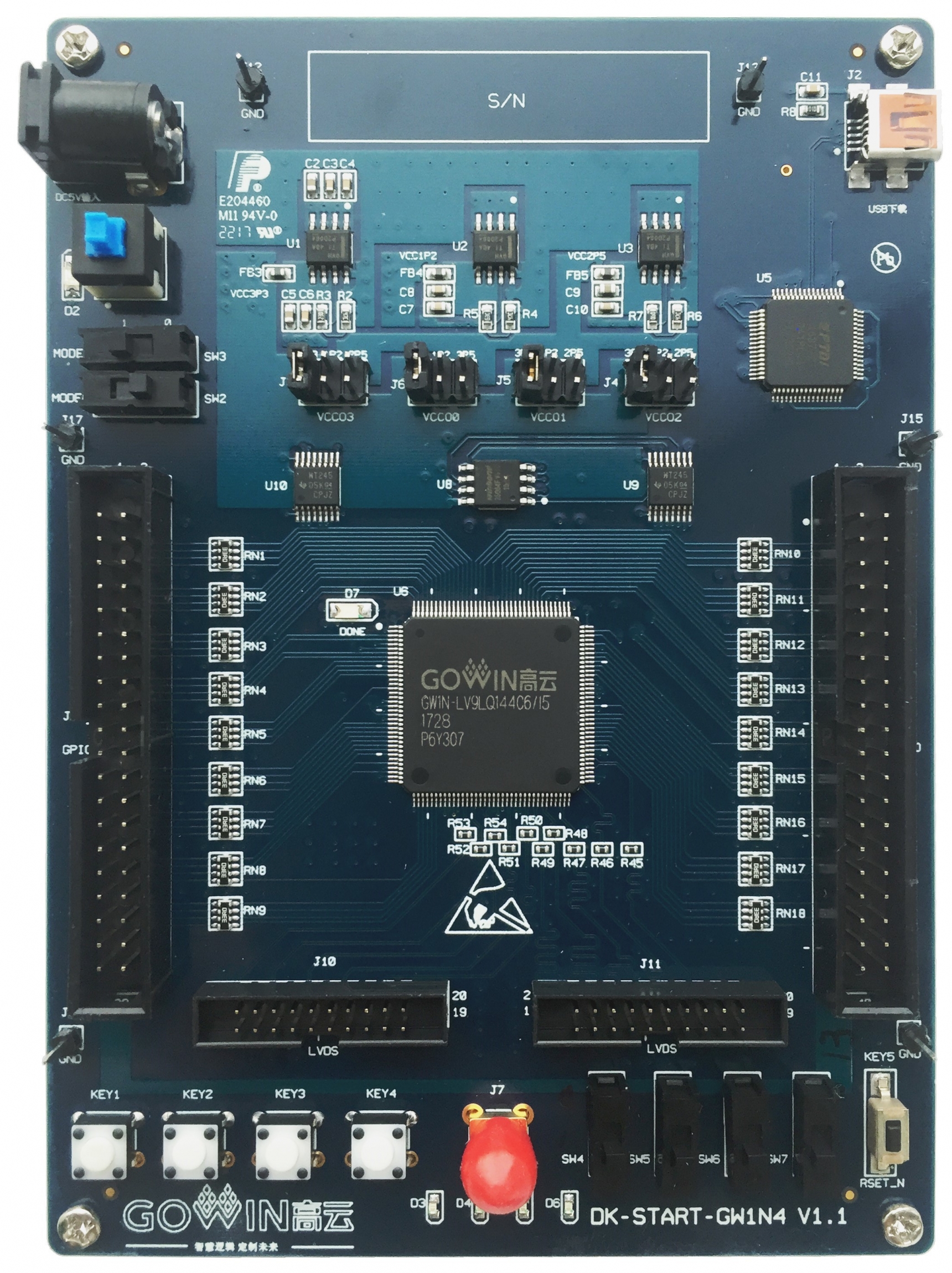

GW1N-9 FPGA

GW1N-9 IO block integrates a new enhanced configuration IO circuitry which is designed to meet MIPI I3C specification; and these enhanced IO circuitry is on two banks of GW1N-9 IO blocks. Users do not need to make any change on software when using such enhanced IO circuitry. The only thing need to do is to enable I3C mode in the PNR constraints for GOWIN YunYuanÒ EDA.

GWI3C IP Development Board and Reference Design

On top of GWI3C IP, GOWIN provides full function I3C development board for customer to develop I3C application off the shelf. Moreover, the I3C development board is designed to be stackable and can be used to communicate with multiple devices at the same I3C bus.