## Gowin USB 1.1 SoftPHY IP

## **User Guide**

IPUG759-1.2.1E, 11/16/2022

Copyright © 2023 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

**GOWIN** is a trademark of Guangdong Gowin Semiconductor Corporation and is registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders. No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

#### **Revision History**

| Date       | Version | Description                                                                                                                                |  |

|------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| 01/06/2021 | 1.0E    | Initial version published.                                                                                                                 |  |

| 04/09/2021 | 1.1E    | Chapter 3 Functional Description modified.                                                                                                 |  |

| 09/02/2022 | 1.2E    | <ul><li>The description of resource utilization added.</li><li>Clock parameter configuration modified.</li></ul>                           |  |

| 11/16/2023 | 1.2.1E  | The descriptions of Figure 3-3 USB Slave Device Interface Implementation and Figure 3-4 USB Slave Device Interface Implementation updated. |  |

## **Contents**

| Coı  | ntents                             | i    |

|------|------------------------------------|------|

| Lis  | t of Figures                       | . ii |

| Lis  | t of Tables                        | iii  |

| 1 A  | bout This Guide                    | . 1  |

|      | 1.1 Purpose                        | 1    |

|      | 1.2 Related Documents              | 1    |

|      | 1.3 Terminology and Abbreviations  | 2    |

|      | 1.4 Support and Feedback           | 2    |

| 2 In | ntroduction                        | . 3  |

|      | 2.1 Overview                       | 3    |

|      | 2.2 Features                       | 3    |

|      | 2.3 Resource Utilization           | 3    |

| 3 F  | unctional Description              | . 5  |

|      | 3.1 USB 1.1 SoftPHY                | 5    |

| 4 S  | ignal Description                  | . 8  |

|      | 4.1 Signal Description             | 8    |

|      | 4.2 Parameter Configuration Option | 9    |

| 5 In | nterface Configuration             | 10   |

## **List of Figures**

| Figure 3-1 SoftPHY Block Diagram                      | 5  |

|-------------------------------------------------------|----|

| Figure 3-2 USB Master Device Interface Implementation | 6  |

| Figure 3-3 USB Slave Device Interface Implementation  | 6  |

| Figure 3-4 USB Slave Device Interface Implementation  | 7  |

| Figure 5-1 IP Core Generator                          | 10 |

| Figure 5-2 Open USB 1.1 SoftPHY IP Core               | 11 |

| Figure 5-3 USB 1.1 SoftPHY IP Configuration Interface | 11 |

IPUG759-1.2.1E ii

## **List of Tables**

| Table 1-1 Terminology and Abbreviations | . 2 |

|-----------------------------------------|-----|

| Table 2-1 Resource Utilization          | . 3 |

| Table 4-1 Signals Description           | . 8 |

| Table 4-2 Configuration Option          | . 9 |

IPUG759-1.2.1E iii

1 About This Guide 1.1 Purpose

## 1 About This Guide

#### 1.1 Purpose

The purpose of Gowin USB 1.1 SoftPHY IP User Guide is to help you learn the features and usage of Gowin USB 1.1 SoftPHY IP by providing descriptions of signals, functions and interface configuration.

#### 1.2 Related Documents

The latest user guides are available on the GOWINSEMI Website. You can find the related documents at www.gowinsemi.com:

- DS100, GW1N series of FPGA Products Data Sheet

- DS117, GW1NR series of FPGA Products Data Sheet

- DS891, GW1NRF series of FPGA Products Data Sheet

- DS821, GW1NS series of FPGA Products Data Sheet

- DS871, GW1NSE series of FPGA Products Data Sheet

- DS881, GW1NSER series of FPGA Products Data Sheet

- DS861, GW1NSR series of FPGA Products Data Sheet

- DS102, GW2A series of FPGA Products Data Sheet

- DS226, GW2AR series of FPGA Products Data Sheet

- SUG100, Gowin Software User Guide

IPUG759-1.2.1E 1(11)

### 1.3 Terminology and Abbreviations

The terminology and abbreviations used in this manual are as shown in Table 1-1.

**Table 1-1 Terminology and Abbreviations**

| Terminology and Abbreviations | Meaning                                 |

|-------------------------------|-----------------------------------------|

| FS                            | Full Speed                              |

| HS                            | High Speed                              |

| IP                            | Intellectual Property                   |

| LS                            | Low Speed                               |

| USB                           | General Serial Bus                      |

| UTMI                          | USB 2.0 Transceiver Macrocell Interface |

### 1.4 Support and Feedback

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly by the following ways.

Website: www.gowinsemi.com

E-mail: <a href="mailto:support@gowinsemi.com">support@gowinsemi.com</a>

IPUG759-1.2.1E 2(11)

2 Introduction 2.1 Overview

## 2 Introduction

#### 2.1 Overview

Gowin USB 1.1 SoftPHY IP is a USB physical layer transceiver that can support data receiving and transmitting at full speed (12 Mbps) or low speed (1.5 Mbps).

#### 2.2 Features

The features of USB 1.1 SoftPHY IP include:

- Supports Full Speed Mode (12 Mbps) and Low Speed Mode (1.5 Mbps)

- Supports data serial and parallel conversion

- Supports bit stuffing and extraction

- Supports NRZI encoding and decoding

- Supports UTMI interface

#### 2.3 Resource Utilization

Gowin USB 1.1 SoftPHY IP can be implemented by Verilog language. Its resource utilization may vary when the design is employed in different devices, or at different densities, speed grades. Taking Gowin GW1N-2 series of products for an instance, the resource utilization of USB 1.1 SoftPHY is shown in Table 2-1.

**Table 2-1 Resource Utilization**

| Device Series | Speed Grade | Name | Resource Utilization | Note |

|---------------|-------------|------|----------------------|------|

| CWAN          | E           | LUT  | 133                  | _    |

| GW1N-2        | <b>-</b> 5  | REG  | 47                   |      |

IPUG759-1.2.1E 3(11)

2 Introduction 2.3 Resource Utilization

| Device Series | Speed Grade | Name  | Resource Utilization | Note |

|---------------|-------------|-------|----------------------|------|

|               |             | ALU   | 0                    |      |

|               |             | BSRAM | 0                    |      |

|               |             | Ю     | 2                    |      |

IPUG759-1.2.1E 4(11)

3 Functional Description 3.1 USB 1.1 SoftPHY

# 3 Functional Description

#### 3.1 USB 1.1 SoftPHY

In the RX direction, after USB serial data goes through the modules including CDR, NRZI decoding, bit extraction, data shifting, the realized USB RX data is received, and the received data is sent to the upper module through the UTMI interface. In the TX direction, after receiving the transmit data, the USB serial data goes through the modules including data shifting, bit filling, NRZI encoding to generate the serial TX data stream.

Data+

Data

Data

RX CDR NRZI Bit Shift Reg UTMI

RX State Machine

RX State Machine

Figure 3-1 SoftPHY Block Diagram

USB 1.1 SoftPHY supports Full Speed Mode (12Mbps) and Low Speed

IPUG759-1.2.1E 5(11)

3 Functional Description 3.1 USB 1.1 SoftPHY

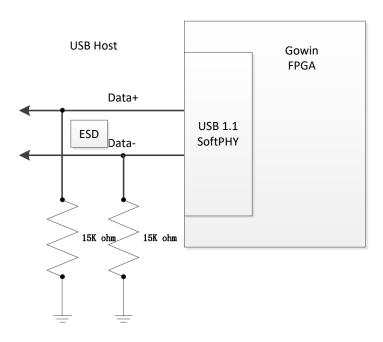

Mode (1.5Mbps); When USB 1.1 SoftPHY is used as the master device, a 15K pull-down resistor needs to be connected to Data+ and Data-.

Figure 3-2 USB Master Device Interface Implementation

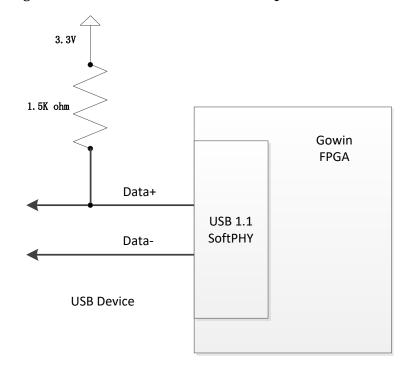

When USB 1.1 SoftPHY is used as the slave device in full speed, a 1.5K pull-up resistor needs to be connected to Data+.

Figure 3-3 USB Slave Device Interface Implementation

IPUG759-1.2.1E 6(11)

3 Functional Description 3.1 USB 1.1 SoftPHY

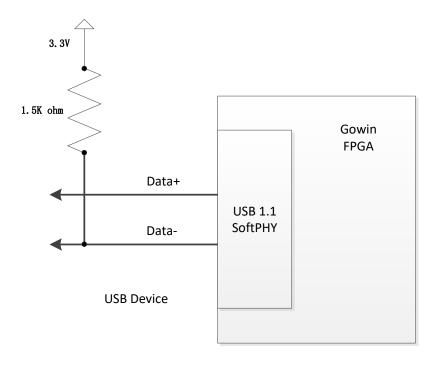

When USB 1.1 SoftPHY is used as the slave device in low speed, a 1.5K pull-up resistor needs to be connected to Data-.

Figure 3-4 USB Slave Device Interface Implementation

IPUG759-1.2.1E 7(11)

## 4 Signal Description

## 4.1 Signal Description

The descriptions of signals are as shown in Table 4-1.

**Table 4-1 Signals Description**

| No. | Signal Name       | I/O | Data Width | Description                                                                                                                                                                                                                                  | Note |

|-----|-------------------|-----|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1   | clk_i             | I   | 1          | Input clock signal (36MHz/48MHz/60MHz)                                                                                                                                                                                                       |      |

| 2   | rst_i             | I   | 1          | Asynchronous reset signal; reset the state machine inside of PHY                                                                                                                                                                             |      |

| 3   | utmi_data_out_i   | Ι   | 8          | Data input, 8-bit parallel TX data bus                                                                                                                                                                                                       |      |

| 4   | utmi_txvalid_i    | I   | 1          | TX data valid, active-high                                                                                                                                                                                                                   |      |

| 5   | utmi_opmode_i     | I   | 2          | <ul> <li>Operation mode selection signal:</li> <li>2'b00: Normal</li> <li>2'b01: No driver</li> <li>2'b10: Disable bit stuffing and NRZI encoding</li> <li>2'b11: Operation of not automatically generating start and end signals</li> </ul> | _    |

| 6   | utmi_xcvrselect_i | I   | 2          | <ul> <li>Transmit mode selection signal:</li> <li>2'b00: HS transmission (Not supported)</li> <li>2'b01: FS transmission</li> <li>2'b10: LS transmission</li> <li>2'b11: Reserved</li> </ul>                                                 |      |

| 7   | utmi_termselect_i | ı   | 1          | Termination selection:                                                                                                                                                                                                                       |      |

IPUG759-1.2.1E 8(11)

| No. | Signal Name      | I/O | Data Width | Description                                                                                                      | Note |

|-----|------------------|-----|------------|------------------------------------------------------------------------------------------------------------------|------|

|     |                  |     |            | <ul> <li>1' b0: HS termination enable (Not supported)</li> <li>1' b1: FS/LS termination enable</li> </ul>        |      |

| 8   | utmi_data_in_o   | 0   | 8          | Data Output, 8-bit parallel RX data bus                                                                          |      |

| 9   | utmi_txready_o   | 0   | 1          | TX data ready signal, indicating that PHY can receive this data                                                  |      |

| 10  | utmi_rxactive_o  | 0   | 1          | RX data activation, indicating that the receive state machines detects the SYNC signal and starts receiving data |      |

| 11  | utmi_rxvalid_o   | 0   | 1          | RX data valid, active-high                                                                                       |      |

| 12  | utmi_rxerror_o   | 0   | 1          | RX data error; active-high indicates receive error                                                               |      |

| 13  | utmi_linestate_o | 0   | 2          | Line status of receive: DM DP  2'b00: SE0 2'b01: "J" status 2'b10: "K" status 2'b11: SE1                         |      |

| 14  | usb_dp_io        | I/O | 1          | USB data signal Data+                                                                                            |      |

| 15  | usb_dn_io        | I/O | 1          | USB data signal Data-                                                                                            |      |

## 4.2 Parameter Configuration Option

Gowin USB 1.1 SoftPHY IP parameter configuration is shown in Table 4-2.

**Table 4-2 Configuration Option**

| Option          | Description                                             |

|-----------------|---------------------------------------------------------|

| Clock Frequency | Working clock frequency includes 36MHz, 48MHz and 60MHz |

IPUG759-1.2.1E 9(11)

# 5 Interface Configuration

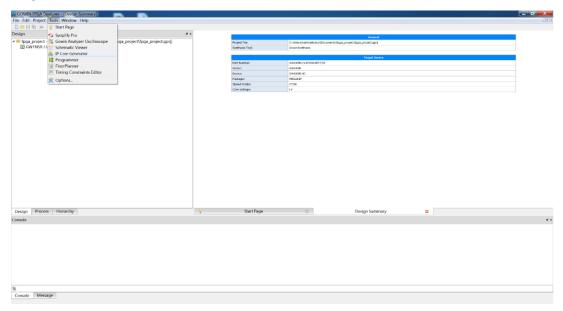

Select "Tools" in the Gowin Software interface, and you can start the IP Core Generator tool, call and configure USB 1.1 SoftPHY.

#### 1. Open IP Core Generator

After creating the project, you can click the "Tools" tab in the upper left, select and open the IP Core Generator via the drop-down list, as shown in Figure 5-1.

Figure 5-1 IP Core Generator

#### 2. Open USB 1.1 SoftPHY IP Core

Select "Soft IP Core > Interface and Interconnect > USB 1.1 IP", as shown in Figure 5-2. Double click to open the configuration interface.

IPUG759-1.2.1E 10(11)

a te del hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works High

| See | See | Hyper bolo Works Hig

Figure 5-2 Open USB 1.1 SoftPHY IP Core

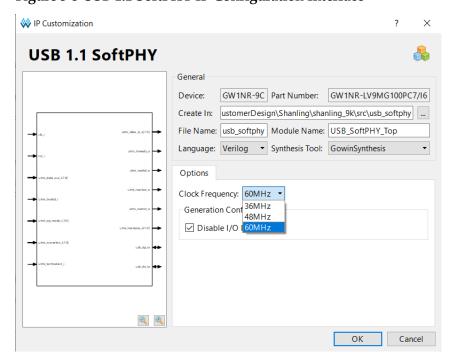

#### 3. USB 1.1 SoftPHY IP Core Configuration Interface

Figure 5-3 shows the USB 1.1 SoftPHY IP core configuration interface. The interface diagram is on the left. Options are on the right.

- You can configure the file name in "File Name"

- You can configure the top module name in "Module Name"

- You can configure the speed mode, power supply mode, endpoint transmission type in "Options".

Figure 5-3 USB 1.1 SoftPHY IP Configuration Interface

IPUG759-1.2.1E 11(11)