## Gowin SDIO Slave Controller **User Guide**

IPUG905-1.0E, /11/08/2019

#### Copyright<sup>©</sup>2019 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI<sup>®</sup>, LittleBee<sup>®</sup>, Arora, and the GOWINSEMI logos are trademarks of GOWINSEMI and are registered in China, the U.S. Patent and Trademark Office, and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders, as described at www.gowinsemi.com. GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. All information in this document should be treated as preliminary. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

## **Revision History**

| Date       | Version | Description                |

|------------|---------|----------------------------|

| 11/08/2019 | 1.0E    | Initial version published. |

## Contents

| Contents                               | i   |

|----------------------------------------|-----|

| List of Figures                        | iii |

| List of Tables                         | iv  |

| 1 About This Guide                     | .1  |

| 1.1 Purpose                            | 1   |

| 1.2 Supported Products                 | 1   |

| 1.3 Related Documents                  | 1   |

| 1.4 Terminology and Abbreviations      | 1   |

| 1.5 Support and Feedback               | 2   |

| 2 Overview                             | .3  |

| 3 Features and Performance             | . 4 |

| 3.1 Key Features                       | 4   |

| 3.2 Working Frequency                  | 4   |

| 3.3 Resource Utilization               |     |

| 4 Structure and Functional Description | . 6 |

| 4.1 Overall Structure                  | 6   |

| 4.2 Definition of SDIO Interface       | 6   |

| 4.2.1 Circuit Connection               | 7   |

| 4.3 Non UHS Card and UHS-I Card        | 8   |

| 4.3.1 Non UHS Card                     | 8   |

| 4.3.2 UHS-I Card                       | 8   |

| 4.4 SDIO Initialization                |     |

| 4.4.1 Non UHS Card Initialization Flow |     |

| 4.4.2 UHS-I Card Initialization Flow   |     |

| 4.5 CIA (Function0) Register           |     |

| 4.6 CMD52                              |     |

|                                        |     |

| 4.8 Abort                              |     |

| 4.9 CMD19                              |     |

| 4.10 Interrupt Function                |     |

| 4.10.1 Interrupt Generation            |     |

| 4.11 User Interface                    |     |

| 4.11.1 CPU Slave Interface   |    |

|------------------------------|----|

| 4.11.2 SDIO CMD52 Interface  | 21 |

| 4.11.3 SDIO CMD53 Interface  | 24 |

| 4.11.4 SDIO Tuning Interface | 31 |

| 5 Port List                  | 32 |

| 6 Initialization             |    |

| 6.1 IP Initialization Flow   |    |

| 7 Interface Configuration    | 38 |

| 8 Parameter Configuration    | 40 |

| 9 Reference Design           | 41 |

## **List of Figures**

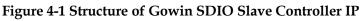

| Figure 4-1 Structure of Gowin SDIO Slave Controller IP                 | . 6  |

|------------------------------------------------------------------------|------|

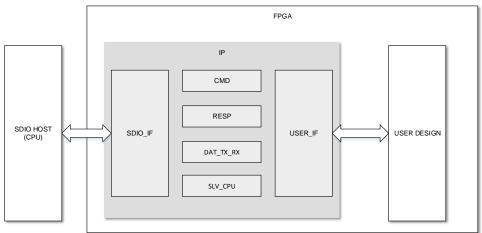

| Figure 4-2 Schematic Diagram of SDIO Pin Connection                    | . 8  |

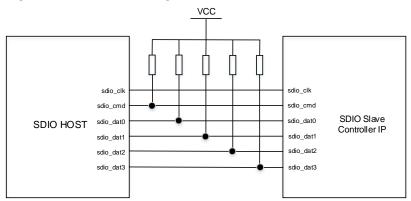

| Figure 4-3 Non UHS Card Initialization Flow                            | . 9  |

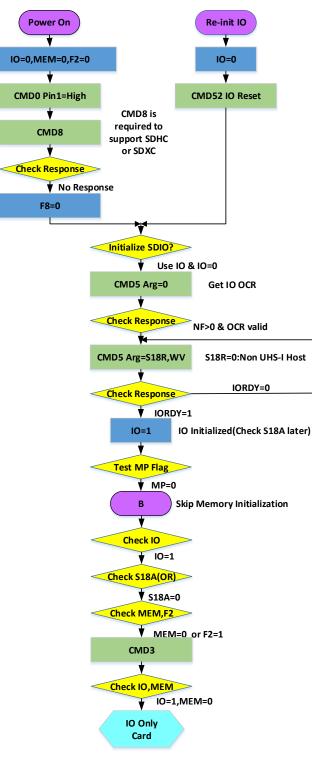

| Figure 4-4 UHS-I Card Initialization Flow                              | . 10 |

| Figure 4-5 Tuning Block Pattern                                        | . 12 |

| Figure 4-6 Write Timing of CPU Slave Interface                         | . 19 |

| Figure 4-7 Read Timing of CPU Slave Interface                          | . 20 |

| Figure 4-8 Read and Write Alternatively Timing of CPU Slave Interface  | . 20 |

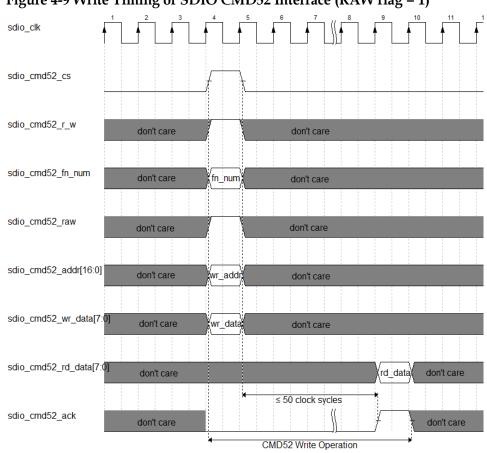

| Figure 4-9 Write Timing of SDIO CMD52 Interface (RAW flag = 1)         | . 22 |

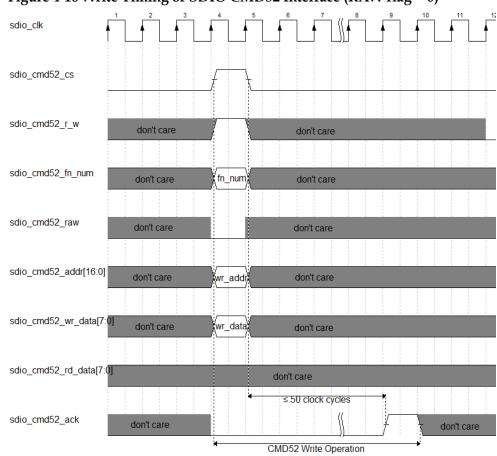

| Figure 4-10 Write Timing of SDIO CMD52 Interface (RAW flag = 0)        | . 23 |

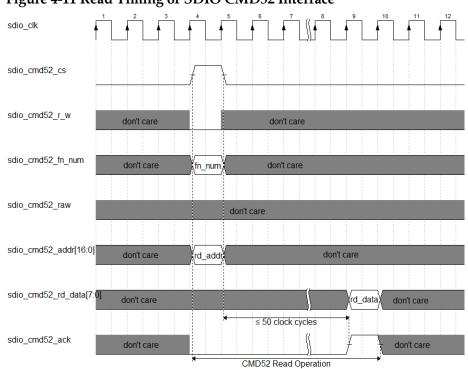

| Figure 4-11 Read Timing of SDIO CMD52 Interface                        | . 24 |

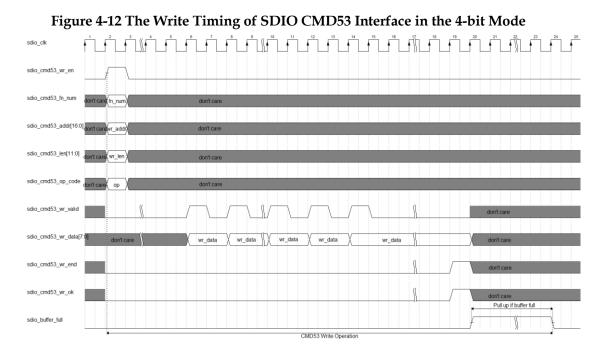

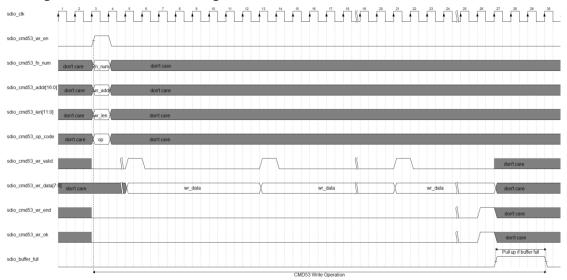

| Figure 4-12 The Write Timing of SDIO CMD53 Interface in the 4-bit Mode | . 26 |

| Figure 4-13 The Write Timing of SDIO CMD53 Interface in the 1-bit Mode | . 26 |

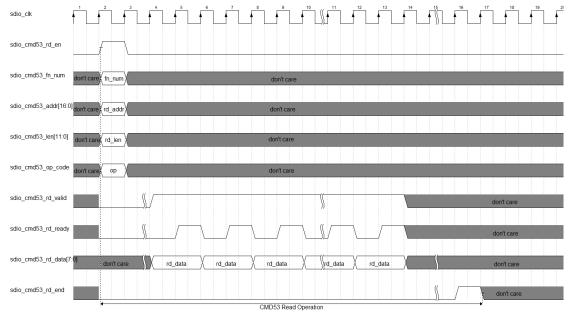

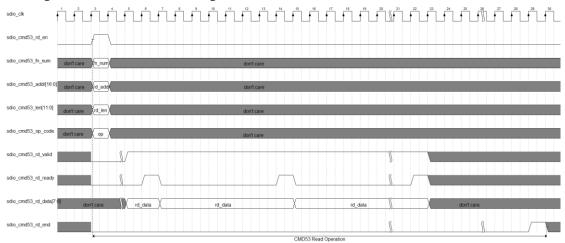

| Figure 4-14 The Read Timing of SDIO CMD53 Interface in the 4-bit Mode  | . 27 |

| Figure 4-15 The Read Timing of SDIO CMD53 Interface in the 1-bit Mode  | . 27 |

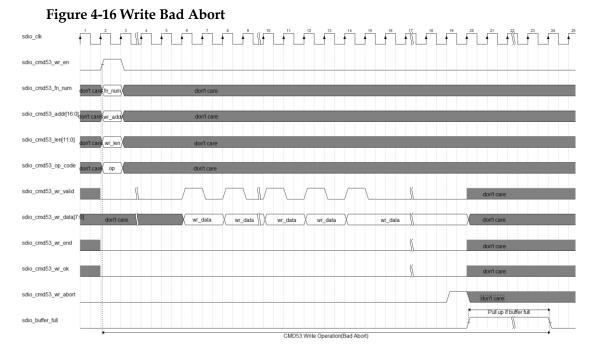

| Figure 4-16 Write Bad Abort                                            | . 28 |

| Figure 4-17 Write Good Abort Case1                                     | . 29 |

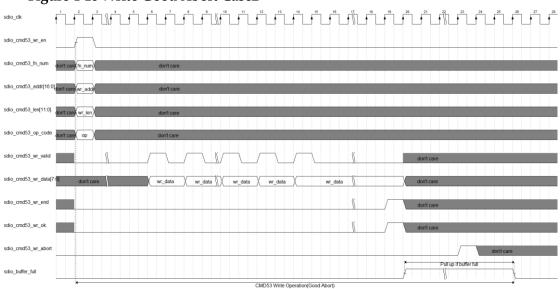

| Figure 4-18 Write Good Abort Case2                                     | . 29 |

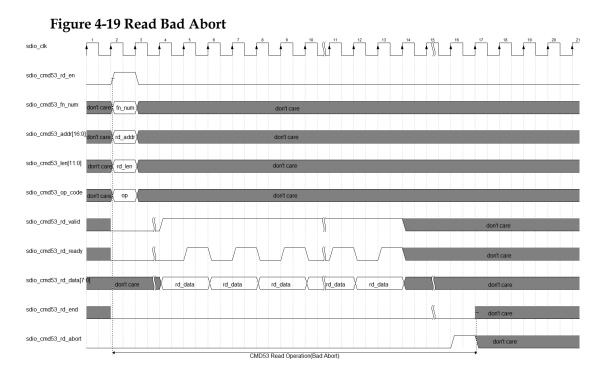

| Figure 4-19 Read Bad Abort                                             | . 30 |

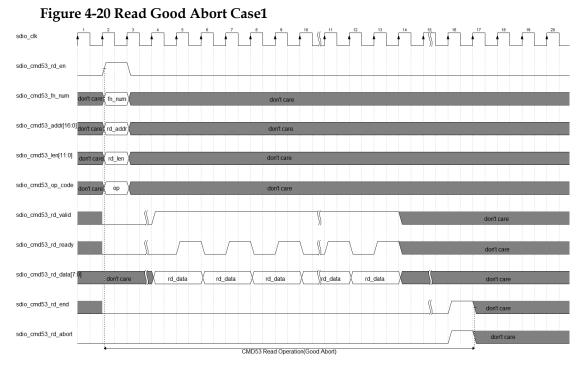

| Figure 4-20 Read Good Abort Case1                                      | . 30 |

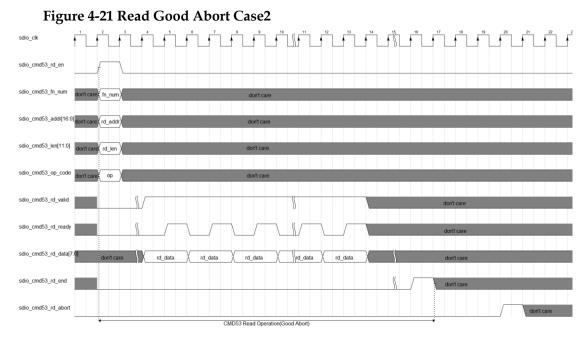

| Figure 4-21 Read Good Abort Case2                                      | . 31 |

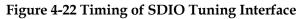

| Figure 4-22 Timing of SDIO Tuning Interface                            | . 31 |

| Figure 7-1 IP Core Generator Tool                                      | . 38 |

| Figure 7-2 Configuration Interface of SDIO Slave Controller IP         | . 39 |

| Figure 7-3 Help                                                        | . 39 |

## List of Tables

| Table 1-1 Terminology and Abbreviations                                             | 1  |

|-------------------------------------------------------------------------------------|----|

| Table 2-1 Gowin SDIO Slave Controller IP                                            | 3  |

| Table 3-1 Resource Utilization                                                      | 5  |

| Table 4-1 Interface Definition Relationship between SDIO Slave Controller IP and SD | 7  |

| Table 4-2 Register Definition of CPU Slave Interface                                | 13 |

| Table 5-1 IO Ports of Gowin SDIO Slave Controller IP                                | 32 |

| Table 8-1 Static and Tming Parameters of Gowin SDIO Slave Controller                | 40 |

# **1** About This Guide

### 1.1 Purpose

This Gowin SDIO Slave Controller IP user guide aims to help users quickly learn the functions of Gowin SDIO Slave Controller and quickly understand the features and usage of the Gowin SDIO Slave Controller IP.

## **1.2 Supported Products**

The information presented in this guide applies to the following products:

- GW1N series of FPGA Products

- GW1NR series of FPGA Products

- GW2A series of FPGA Products

- GW2AR series of FPGA Products

## **1.3 Related Documents**

The user guides are available on the GOWINSEMI Website. You can find the related documents at <u>www.gowinsemi.com</u>:

- 1. <u>DS100</u>, GW1N series of FPGA Products Data Sheet

- 2. DS117, GW1NR series of FPGA Products Data Sheet

- 3. <u>DS102</u>, GW2A series of FPGA Products Data Sheet

- 4. DS226, GW2AR series of FPGA Products Data Sheet

- 5. <u>SUG100</u>, Gowin YunYuan Software User Guide

## **1.4 Terminology and Abbreviations**

The terminology and abbreviations used in this manual are as shown in Table 1-1.

Table 1-1 Terminology and Abbreviations

| Terminology and Abbreviations | Meaning                         |  |  |

|-------------------------------|---------------------------------|--|--|

| IP                            | Intellectual Property           |  |  |

| LUT                           | Look-up Table                   |  |  |

| SDIO                          | Secure Digital Input and Output |  |  |

## **1.5 Support and Feedback**

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly by the following ways.

Website: www.gowinsemi.com

E-mail: support@gowinsemi.com

+Tel: +86 755 8262 0391

# 2<sub>Overview</sub>

This document describes the Gowin SDIO Slave Controller IP and provides the user with a general interface of SDIO Slave. Users can integrate this IP into SDIO designs to implement the functions of an SDIO device. It can be integrated into devices that require SDIO Slave and this interface can be applied to a wide range of applications.

| Gowin SDIO Slave Controller IP |                                                                                                                                                     |  |  |  |

|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Supported Devices              | GW1N-4, GW1N-4B, GW1N-6, GW1N-9,<br>GW1NR-4, GW1NR-4B, GW1NR-9, GW1NS-4,<br>GW1NS-4C, GW1NSR-4, GW1NSER-4C,<br>GW1NRF-4B, GW2A series, GW2AR series |  |  |  |

| Logic Resource                 | See Table 3-1.                                                                                                                                      |  |  |  |

| Delivered Doc.                 |                                                                                                                                                     |  |  |  |

| Design Files                   | Verilog (encryption)                                                                                                                                |  |  |  |

| Reference Design               | Verilog                                                                                                                                             |  |  |  |

| TestBench                      | Verilog                                                                                                                                             |  |  |  |

| Test and Design Flow           |                                                                                                                                                     |  |  |  |

| Synthesis Software             | Synplify_Pro                                                                                                                                        |  |  |  |

| Application Software           | Gowin YunYuan ( V1.9.2.02Beta )                                                                                                                     |  |  |  |

# **3**<sub>Features</sub> and Performance

### **3.1 Key Features**

- Supports SD Physical Layer Specification Version 4.00;

- Supports SDIO Specification Version 4.00;

- Supports 1-bit and 4-bit SD transfer modes;

- SPI transfer mode is not supported;

- Supports Low-Speed and Full-Speed modes; The highest speed supported is 25MB/sec;

- Supports UHS-I mode and rates of SDR12, SDR25 and SDR50

- UHS-I mode supports 1.8V voltage and voltage switching is not supported

- Supports SDIO Command types: CMD0, CMD3, CMD5, CMD7, CMD11, CMD15, CMD19, CMD52, CMD53

- Supports automatic generation and validation of CRC7 and CRC16

- Supports Function 0 and Function1

- Supports configuring IP using CPU Slave interface of user side

- Supports CMD 52 and CMD53 interfaces of user side

- Supports interrupts of 1-bit mode and 4-bit mode, and the interrupt of 4bit mode doesn't support Data Block Gap and Asynchronous Interrupt

- Supports write abort and read abort

- Suspend/Resume functions are not supported;

- Read Wait function is not supported;

- Combo Card is not supported;

- CSA is not supported;

- DDR mode is not supported;

- Card Detection is not supported.

## 3.2 Working Frequency

The working frequency of Gowin SDIO Slave Controller IP depends on the clock frequency of the Gowin SDIO Host and the maximum working frequency supported by the IP on the selected chip.

## 3.3 Resource Utilization

Gowin SDIO Slave Controller IP adopts Verilog, which applies in GW1N series, GW1NR series, GW2A series and GW2AR series FPGA devices. Different modes have different resource consumption. An overview of resource utilization is given in Table 3-1. For the resource utilization of other devices, please refer to the post release information.

| Table 3-1 Resource | Utilization |

|--------------------|-------------|

|--------------------|-------------|

| Туре    | LUTs | REGs | Device Series | Speed Level |

|---------|------|------|---------------|-------------|

| Non UHS | 3216 | 1566 | GW2A18        | -8          |

| UHS-I   | 3214 | 1587 | GW2A18        | -8          |

# **4** Structure and Functional Description

## 4.1 Overall Structure

The basic structure of Gowin SDIO Slave Controller IP is shown in Figure 4-1, mainly including modules such as SDIO\_IF, CMD, RESP, DAT\_TX\_RX, SLV\_CPU and USER\_IF. The User Design in the figure refers to the User Design in the FPGA, and the SDIO HOST is the SDIO host.

- SDIO\_IF module realizes data selection of SDIO interface and bi-directional transfer;

- CMD module realizes the analysis function of SDIO Command;

- RESP module realizes the generation function of SDIO Response;

- DAT\_TX\_RX module realizes CMD19 and CMD 53 data read and write;

- SLV\_CPU module realizes user configuring IP function;

- USE\_IF module realizes data exchange between user side and IP.

## **4.2 Definition of SDIO Interface**

The corresponding relationship between SDIO Slave Controller IP interface definition and SD interface definition is shown in Table 4-1.

| Pin  | SD            | IP                          |               |                |                                                |

|------|---------------|-----------------------------|---------------|----------------|------------------------------------------------|

| PIII | SD 4-bit mode |                             | SD 1-bit mode |                | 1F                                             |

| 1    | CD/DAT[3]     | Data line 3                 | N/C           | Not Used       | sdio_dat3_in<br>sdio_dat3_out<br>sdio_dat3_oen |

| 2    | CMD           | Command line                | CMD           | Command line   | sdio_cmd_in<br>sdio_cmd_out<br>sdio_cmd_oen    |

| 3    | VSS1          | Ground                      | VSS1          | Ground         | -                                              |

| 4    | VDD           | Supply voltage              | VDD           | Supply voltage | -                                              |

| 5    | CLK           | Clock                       | CLK           | Clock          | sdio_clk                                       |

| 6    | VSS2          | Ground                      | VSS2          | Ground         | -                                              |

| 7    | DAT[0]        | Data line 0                 | DATA          | Data line      | sdio_dat0_in<br>sdio_dat0_out<br>sdio_dat0_oen |

| 8    | DAT[1]        | Data line 1 or<br>Interrupt | IRQ           | Interrupt      | sdio_dat1_in<br>sdio_dat1_out<br>sdio_dat1_oen |

| 9    | DAT[2]        | Data line 2 or<br>Read Wait | RW            | Read Wait      | sdio_dat2_in<br>sdio_dat2_out<br>sdio_dat2_oen |

Table 4-1 Interface Definition Relationship between SDIO Slave Controller IP and<br/>SD

The user can convert SDIO interface defined by IP to the input/output format by the following statements.

assign sdio\_cmd\_in = sdio\_cmd; assign sdio\_cmd = (!sdio\_cmd\_oen) ? sdio\_cmd\_out : 1'bz; assign sdio\_dat0\_in = sdio\_dat0; assign sdio\_dat0 = (!sdio\_dat0\_oen) ? sdio\_dat0\_out : 1'bz; assign sdio\_dat1\_in = sdio\_dat1; assign sdio\_dat1 = (!sdio\_dat1\_oen) ? sdio\_dat1\_out : 1'bz; assign sdio\_dat2\_in = sdio\_dat2; assign sdio\_dat2 = (!sdio\_dat2\_oen) ? sdio\_dat2\_out : 1'bz; assign sdio\_dat3\_in = sdio\_dat3; assign sdio\_dat3 = (!sdio\_dat3\_oen) ? sdio\_dat3\_out : 1'bz;

#### 4.2.1 Circuit Connection

When the circuit is connected, the CMD and DAT wires need to be connected to the VCC through a pull-up resistor. When the IP is set to Non UHS Card, VCC is 3.3v; When the IP is set to UHS-I Card, VCC is 1.8v. The reference circuit is as shown in Figure 4-2.

Figure 4-2 Schematic Diagram of SDIO Pin Connection

## 4.3 Non UHS Card and UHS-I Card

IP supports Non UHS Card and UHS-I Card. Users need to configure the interface to generate IP.

#### 4.3.1 Non UHS Card

When IP works on non-uhs Card, the voltage of Bank and the pull-up resistor on SDIO interface should be 3.3v.

Non UHS Card supports low-speed and full-speed. Full-speed supports default-speed and high-speed.

After the user configures IP to Non UHS Card, in the initialization stage, no matter whether IP receives CMD5 S18R as 0 or 1, S18A in IP response R4 is always 0. IP does not support CMD11 and CMD19 when IP works on Non UHS Card.

#### 4.3.2 UHS-I Card

When IP works on UHS-I Card, the voltage of bank and pull-up resistor on SDIO interface should be 1.8v.

UHS-I Card supports SDR12, SDR25 and SDR50.

After the user configures IP to UHS-I Card, in the initialization stage, when IP receives CMD5 S18R as 0, S18A in IP response R4 is 0. When IP receives CMD5 S18R as 1, S18A in IP response R4 is 1. IP supports CMD11 and CMD19 when IP works on UHS-I Card. It should be noted that when IP receives CMD11, it will respond to R1 and support Voltage Switch Sequence without changing the IO Voltage.

## 4.4 SDIO Initialization

IP needs to be initialized by SDIO Host after power on before it can work. The initialization flow complies with SDIO standard. The initialized clock frequency is 100KHz~400KHz.

Since the IP does not support SPI mode, when CMD0 is received during initialization, the IP will remain in SD mode no matter whether sdio\_dat3 is at high level or not.

When the IP is set to UHS-I Card, IP enters to the Voltage Switch Sequence through CMD11 without changing the IO Voltage. When the Voltage Switch Sequence ends, IP enters to the UHS-I state.

### 4.4.1 Non UHS Card Initialization Flow

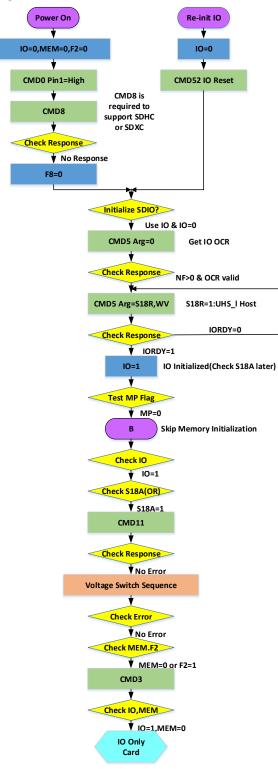

Non UHS Card initialization flow is as shown in Figure 4-3. Figure 4-3 Non UHS Card Initialization Flow

#### 4.4.2 UHS-I Card Initialization Flow

UHS-I Card initialization flow is as shown in Figure 4-4.

**Figure 4-4 UHS-I Card Initialization Flow**

## 4.5 CIA (Function0) Register

The SDIO standard defines CIA register that allows host to read slave status and configure slave function. The host can read and write CIA register through the CMD52 and CMD53 commands.

The CIA register includes CCCR register, FBR register, CIS register, and CSA register.

CCCR register and FBR (Function1) register have been implemented in IP. Users can access the corresponding register through the CPU Slave Interface in the initialization stage. When the host reads and writes the register in this part, the user does not need to participate.

The FBR (Function2~7) register does not support access temporarily. CIS register is not implemented in IP. When host accesses register in this part, the user is required to provide data on SDIO CMD52 interface or SDIO CMD53 interface.

The CSA register does not support access temporarily.

## 4.6 CMD52

When the IP enters into Command State, the host can access the IP register as a single byte through CMD52. Since IP supports Function 0 and Function1, the IP only responds to host for CMD52 of Function0 and Function1.

When host accesses the CCCR and FBR registers through CMD52, IP responds automatically. The user does not to participate.

When host accesses CIS and Function1 registers through CMD52, the user needs to send and receive data through the SDIO CMD52 interface.

## 4.7 CMD53

When the IP enters into Command State, the host can access the IP register continuously through the CMD53 command. Since IP supports Function 0 and Function1, the IP only responds to host for CMD53 of Function 0 and Function1.

When host accesses the CCCR and FBR registers through CMD53, IP responds automatically. The user does not need to participate.

When host accesses CIS and Function1 registers through CMD53, the user needs to send and receive data through SDIO CMD53 interface.

## 4.8 Abort

When host sends CMD53 to read and write data in Infinite Block Mode, the read and write can be interrupted by Abort sent by CMD52.

## 4.9 CMD19

CMD19 is supported when IP is configured to UHS-I Card. IP receives the correct CMD19 and responds to R1 automatically. Users need to provide Tuning Block Pattern through the SDIO Tuning interface. When the IP is configured to Non UHS Card, the user does not need to pay attention to SDIO Tuning interface. There are 144 nibbles in Tuning Block Pattern, as shown in Figure 4-5.

#### **Figure 4-5 Tuning Block Pattern**

```

FF0FFF00_FFCCC3CC_C33CCCFF_FEFFFEEF

FFDFFFDD_FFFBFFFB_BFFF7FFF_77F7BDEF

FFF0FFF0_0FFCCC3C_CC33CCCF_FFEFFFEE

FFFDFFFD_DFFFBFFF_BBFFF7FF_F77F7BDE

F9503A4B_C5488FBC

```

The user needs to send in order from left to right and from top to bottom.

#### **4.10 Interrupt Function**

IP supports interrupts in 1-bit and 4-bit modes.

#### 4.10.1 Interrupt Generation

In 1-bit mode, DAT1 serves as the interrupt signal line. When the user pulls up the fun1\_interrupt pin to 1, DAT1 is pulled down by IP to generate interrupt. The interrupt signal in 1-bit mode is independent of sdio\_clk.

In 4-bit mode, DAT1 serves as the data and interrupt multiplexing signal line. When the user pulls up fun1\_interrupt pin to 1, DAT1 is pulled down by IP in Interrupt Period to generate interrupt. 4-bit mode interrupts do not support Data Block Gap and Asynchronous Interrupt. The interrupt signal in 4-bit mode is synchronized with sdio\_clk. Therefore, when sdio\_clk stops, IP cannot generate an interrupt signal in DAT1. When IP works in 4-bit mode, if the clock needs to stop in SDIO Host design and interrupts are needed to call up the clock, it can be achieved in the following ways:

- 1. Host sets IP to 1-bit mode through CMD52;

- 2. Host stops the clock;

- 3. The user pulls up fun1\_interrupt pin to 1 to generate interrupts in 1-bit mode.

- 4. The Host starts to provide the clock;

- 5. Host sets IP to 4-bit mode through CMD52;

- 6. The Host starts to access IP.

#### **4.10.2** Clear Interrupt

When users detects that the SDIO Host is accessing register clearing interrupt, the user pulls down the fun1\_interrupt pin to 0 to clear the interrupt. The clear interrupt register is defined by user.

The SDIO standard suggests time of clearing interrupt:

If users accesses interrupt clear through CMD52, it needs to clear interrupt before the end of R5;

If users accesses interrupt clear through CMD53, it needs to clear interrupt before the data transfer is completed.

## 4.11 User Interface

### 4.11.1 CPU Slave Interface

#### **CPU Slave Interface Clock**

The CPU Slave Interface clock is cpu\_clk, independent of sdio\_clk. In use, cpu\_clk can connect to sdio\_clk to synchronize clocks on the two interfaces.

#### **CPU Slave Interface Function**

CCCR register and FBR (Function1) register have been implemented in IP. Users can access the corresponding register through the CPU Slave interface in the initialization stage. When the host accesses these registers, users does not need to participate. In addition, users can also set other functions of IP through the CPU Slave interface. The register definition is shown in Table 4-2.

The data interface of CPU Slave interface is 32 bits and the address is aligned with 4 bytes.

#### **Register Definition of CPU Slave Interface**

The register definition of CPU Slave Interface is as shown in Table 4-2.

| Address | Bit     | Name                                  | Default Value | Туре | Description                                                                  |

|---------|---------|---------------------------------------|---------------|------|------------------------------------------------------------------------------|

|         | 3:0     | CCCR/FBR Format<br>Version number     | 0x3           | RO   | CCCR/FBR version<br>Corresponding to CCCR<br>Reg0x0 bit3~bit0                |

|         | 7:4     | SDIO Specification<br>Revision Number | 0x5           | RO   | SDIO version<br>Corresponding to CCCR<br>Reg0x0 bit7~bit4                    |

|         | 11:8    | SD Format Version<br>Number           | 0x4           | RO   | SD version<br>Corresponding to CCCR<br>Reg0x1 bit3~bit0                      |

| 0x00    | 16      | Support Master<br>Power Control       | 0x0           | RW   | Master Power Control<br>Corresponding to CCCR<br>Reg0x12 bit0                |

| 0x00    | 17      | Enable Master Power<br>Control        | 0x0           | RO   | Enable Master Power Control<br>Corresponding to CCCR<br>Reg0x12 bit1         |

|         | 8:18 PM | Total Card Power                      | 0x0           | RO   | Total Card Power<br>Corresponding to CCCR<br>Reg0x12 bit4~bit2               |

|         | 24      | Support High-Speed                    | 0x1           | RW   | Support High-Speed<br>Corresponding to CCCR<br>Reg0x13 bit0                  |

|         | 27:25   | Bus Speed Select                      | 0x0           | RO   | Bus Speed Select<br>Corresponding to CCCR<br>Reg0x13 bit3~bit1               |

| 0x04    | 0       | Interrupt Enable<br>Master            | 0x0           | RO   | Interrupt Enable Master<br>Corresponding to CCCR<br>Reg0x4 bit0              |

|         | 7:1     | Interrupt Enable for<br>Function x    | 0x00          | RO   | Interrupt Enable for Function x<br>Corresponding to CCCR<br>Reg0x4 bit7~bit1 |

Table 4-2 Register Definition of CPU Slave Interface

| Address | Bit | Name                                     | Default Value | Туре | Description                                                                        |

|---------|-----|------------------------------------------|---------------|------|------------------------------------------------------------------------------------|

|         | 9:8 | Bus Width                                | 0x0           | RO   | Bus Width<br>Corresponding to CCCR                                                 |

|         | 10  | Support 8-bit Bus<br>Mode                | 0x0           | RO   | Reg0x7 bit1~bit0<br>Support 8-bit Bus Mode<br>Corresponding to CCCR<br>Reg0x7 bit2 |

|         | 13  | Enable Continuous<br>SPI Interrupt       | 0x0           | RO   | Enable Continuous SPI<br>Interrupt<br>Corresponding to CCCR<br>Reg0x7 bit5         |

|         | 14  | Support Continuous<br>SPI interrupt      | 0x1           | RW   | Support Continuous SPI<br>interrupt<br>Corresponding to CCCR<br>Reg0x7 bit6        |

|         | 15  | Card Detect Disable                      | 0x0           | RO   | Card Detect Disable<br>Corresponding to CCCR<br>Reg0x7 bit7                        |

|         | 16  | Support Direct<br>Command (CMD52)        | 0x1           | RO   | Support Direct Command<br>(CMD52)<br>Corresponding to CCCR<br>Reg0x8 bit0          |

|         | 17  | Support Multiple<br>Block Transfer       | 0x1           | RO   | Support Multiple Block<br>Transfer<br>Corresponding to CCCR<br>Reg0x8 bit1         |

|         | 18  | Support Read Wait                        | 0x0           | RO   | Support Read Wait<br>Corresponding to CCCR<br>Reg0x8 bit2                          |

|         | 19  | Support Bus Control                      | 0x0           | RO   | Support Bus Control<br>Corresponding to CCCR<br>Reg0x8 bit3                        |

|         | 20  | Support Block Gap<br>Interrupt           | 0x0           | RO   | Support Block Gap Interrupt<br>Corresponding to CCCR<br>Reg0x8 bit4                |

|         | 21  | Enable Block Gap<br>Interrupt            | 0x0           | RO   | Enable Block Gap Interrupt<br>Corresponding to CCCR<br>Reg0x8 bit5                 |

|         | 22  | Low-Speed Card                           | 0x0           | RW   | Low-Speed Card<br>Corresponding to CCCR<br>Reg0x8 bit6                             |

|         | 23  | 4-bit Mode Support<br>for Low-Speed Card | 0x0           | RW   | 4-bit Mode Support for<br>Low-Speed Card<br>Corresponding to CCCR<br>Reg0x8 bit7   |

|         | 24  | Support SDR50                            | 0x1           | RW   | Support SDR50<br>Corresponding to CCCR<br>Reg0x14 bit0                             |

|         | 25  | Support SDR104                           | 0x0           | RO   | Support SDR104<br>Corresponding to CCCR<br>Reg0x14 bit1                            |

|         | 26  | Support DDR50                            | 0x0           | RO   | Support DDR50<br>Corresponding to CCCR<br>Reg0x14 bit2                             |

|         | 27  | Support<br>Asynchronous                  | 0x0           | RO   | Support Asynchronous<br>Interrupt                                                  |

| Address | Bit   | Name                             | Default Value | Туре | Description                                                                                                                                                                       |

|---------|-------|----------------------------------|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |       | Interrupt                        |               |      | Corresponding to CCCR<br>Reg0x16 bit0                                                                                                                                             |

|         | 28    | Enable Asynchronous<br>Interrupt | 0x0           | RO   | Enable Asynchronous<br>Interrupt<br>Corresponding to CCCR<br>Reg0x16 bit1                                                                                                         |

| 0x08    | 23:0  | Common CIS Pointer               | 0x001000      | RW   | Common CIS Pointer<br>[23:16] corresponding to<br>CCCR Reg0x0B bit7~bit0<br>[15:8] corresponding to CCCR<br>Reg0x0A bit7~bit0<br>[7:0] corresponding to CCCR<br>Reg0x09 bit7~bit0 |

|         | 24    | Support Driver Type<br>A         | 0x0           | RW   | Support Driver Type A<br>Corresponding to CCCR<br>Reg0x15 bit0                                                                                                                    |

|         | 25    | Support Driver Type<br>C         | 0x0           | RW   | Support Driver Type C<br>Corresponding to CCCR<br>Reg0x15 bit1                                                                                                                    |

|         | 26    | Support Driver Type<br>D         | 0x0           | RW   | Support Driver Type D<br>Corresponding to CCCR<br>Reg0x15 bit2                                                                                                                    |

|         | 29:28 | Driver Type Select               | 0x0           | RO   | Driver Type Select<br>Corresponding to CCCR<br>Reg0x15 bit5~bit4                                                                                                                  |

| 0x0C    | 15:0  | FN0 Block Size                   | 0x0000        | RO   | Function0 Block Size<br>[15:8] corresponding to CCCR<br>Reg0x11 bit7~bit0<br>[7:0] corresponding to CCCR<br>Reg0x10 bit7~bit0                                                     |

| 0x10    | 7:0   | Reserved for Vendors             | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xF0 bit7~bit0                                                                                                                |

|         | 15:8  | Reserved for Vendors             | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xF1 bit7~bit0                                                                                                                |

|         | 23:16 | Reserved for Vendors             | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xF2 bit7~bit0                                                                                                                |

|         | 31:24 | Reserved for Vendors             | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xF3 bit7~bit0                                                                                                                |

| 0x14    | 7:0   | Reserved for Vendors             | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xF4 bit7~bit0                                                                                                                |

|         | 15:8  | Reserved for Vendors             | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xF5 bit7~bit0                                                                                                                |

|         | 23:16 | Reserved for Vendors             | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xF6 bit7~bit0                                                                                                                |

|         | 31:24 | Reserved for Vendors             | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xF7 bit7~bit0                                                                                                                |

| 0x18    | 7:0   | Reserved for Vendors             | 0x00          | RO   | Reserved for Vendors                                                                                                                                                              |

| Address | Bit   | Name                                                 | Default Value | Туре | Description                                                                                                                      |

|---------|-------|------------------------------------------------------|---------------|------|----------------------------------------------------------------------------------------------------------------------------------|

|         |       |                                                      |               |      | Corresponding to CCCR<br>Reg0xF8 bit7~bit0                                                                                       |

|         | 15:8  | Reserved for Vendors                                 | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xF9 bit7~bit0                                                               |

|         | 23:16 | Reserved for Vendors                                 | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xFA bit7~bit0                                                               |

|         | 31:24 | Reserved for Vendors                                 | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xFB bit7~bit0                                                               |

| 0x1C    | 7:0   | Reserved for Vendors                                 | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xFC bit7~bit0                                                               |

|         | 15:8  | Reserved for Vendors                                 | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xFD bit7~bit0                                                               |

|         | 23:16 | Reserved for Vendors                                 | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xFE bit7~bit0                                                               |

|         | 31:24 | Reserved for Vendors                                 | 0x00          | RO   | Reserved for Vendors<br>Corresponding to CCCR<br>Reg0xFF bit7~bit0                                                               |

| 0x20    | 3:0   | Standard SDIO<br>Function Interface<br>Code          | 0xF           | RW   | Standard SDIO Function<br>Interface Code<br>Corresponding to FBR1<br>Reg0x100 bit3~bit0                                          |

|         | 15:8  | Extended Standard<br>SDIO Function<br>Interface Code | 0x00          | RW   | Extended Standard SDIO<br>Function Interface Code<br>Corresponding to FBR1<br>Reg0x101 bit7~bit0                                 |

|         | 23:16 | iSDIO Type Support<br>Code                           | 0x00          | RW   | iSDIO Type Support Code<br>Corresponding to FBR1<br>Reg0x108 bit7~bit0                                                           |

|         | 31:24 | Standard iSDIO<br>Function Interface<br>Code         | 0x00          | RW   | Standard iSDIO Function<br>Interface Code<br>Corresponding to FBR1<br>Reg0x103 bit7~bit0                                         |

| 0x24    | 15:0  | Function 1 I/O Block<br>Size                         | 0x0000        | RO   | Function 1 Block Size<br>[15:8] corresponding to FBR1<br>Reg0x111 bit7~bit0<br>[7:0] corresponding to FBR1<br>Reg0x110 bit7~bit0 |

|         | 16    | Support Power<br>Selection                           | 0x0           | RW   | Support Power Selection<br>Corresponding to FBR1<br>Reg0x102 bit0                                                                |

|         | 20:17 | Power State                                          | 0x0           | RO   | Power State<br>Corresponding to FBR1<br>Reg0x102 bit7~bit4                                                                       |

|         | 21    | Enable Power<br>Selection                            | 0x0           | RO   | Enable Power Selection<br>Corresponding to FBR1<br>Reg0x102 bit1                                                                 |

|         | 24    | Function1 Supports<br>CSA                            | 0x0           | RO   | Support CSA<br>Corresponding to FBR1<br>Reg0x100 bit6                                                                            |

| Address | Bit   | Name                                                        | Default Value | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|-------|-------------------------------------------------------------|---------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 25    | Function1 CSA<br>Enable                                     | 0x0           | RO   | Function1 CSA Enable<br>Corresponding to FBR1<br>Reg0x100 bit7                                                                                                                                                                                                                                                                                                                                               |

| 0x28    | 15:0  | Function1<br>MID_CARD<br>Manufacturer<br>Information        | 0x0000        | RW   | Function1 MID_CARD<br>Manufacturer Information<br>[15:8] corresponding to FBR1<br>Reg0x107 bit7~bit0<br>[7:0] corresponding to FBR1<br>Reg0x106 bit7~bit0                                                                                                                                                                                                                                                    |

|         | 31:16 | Function1<br>SDA_MID_MANF<br>SDIO Card<br>Manufacturer Code | 0x0000        | RW   | Function1 SDA_MID_MANF<br>SDIO Card Manufacturer<br>Code<br>[31:24] corresponding to FBR1<br>Reg0x105 bit7~bit0<br>[23:16] corresponding to FBR1<br>Reg0x104 bit7~bit0                                                                                                                                                                                                                                       |

| 0x2C    | 23:0  | Address pointer to<br>Function1 CIS                         | 0x002000      | RW   | Address pointer to Function1<br>CIS<br>[23:16] corresponding to FBR1<br>Reg0x10B bit7~bit0<br>[15:8] corresponding to FBR1<br>Reg0x10A bit7~bit0<br>[7:0] corresponding to FBR1<br>Reg0x109 bit7~bit0                                                                                                                                                                                                        |

| 0x30    | 0     | IO_Ready                                                    | 0x0           | RW   | IO_Ready<br>This bit corresponding to the C<br>field in R4. After power on, the<br>bit is 0. After the user<br>initializing the register through<br>the CPU Slave interface, set<br>the bit to 1                                                                                                                                                                                                             |

|         | 18:16 | SDIO Bus State                                              | 0x0           | RO   | SDIO Bus State User read IP<br>Bus states through this<br>register.<br>0x0: Idle State, indicating that<br>IP has not completed<br>negotiation with Host through<br>CMD5;<br>0x1: Initialization State,<br>indicating that the IP has<br>completed the negotiation with<br>Host through CMD5;<br>0x2: Standby State<br>0x3: Command State<br>0x4: Transfer State<br>0x5: Inactive State<br>Others: undefined |

|         | 24    | Manual TX Clock to<br>Data Phase                            | 0x0           | RW   | The data sent by SDIO and<br>SDIO clock phase are valid<br>when the Manual TX Clock to<br>Data Phase Enable register is<br>enabled.<br>0: SDIO clock negedge<br>sending data;<br>1: SDIO clock posedge                                                                                                                                                                                                       |

| Address | Bit   | Name                                    | Default Value | Туре | Description                                                                                                                                                                                                                                       |

|---------|-------|-----------------------------------------|---------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |       |                                         |               |      | sending data;                                                                                                                                                                                                                                     |

|         | 25    | Manual TX Clock to<br>Data Phase Enable | 0x0           | RW   | The data sent by SDIO and<br>SDIO clock phase are<br>configured manually to enable<br>1: enable, configure based on<br>the value of Manual TX Clock<br>to Data Phase;<br>0: disable, automatic<br>configuration according to the<br>SDIO standard |

| 0x34    | 15:0  | CCCR Max Block<br>Size                  | 0x0800        | RW   | CCCR Max Block Size                                                                                                                                                                                                                               |

|         | 31:16 | FBR1 Max Block Size                     | 0x0800        | RW   | FBR1 Max Block Size                                                                                                                                                                                                                               |

#### **CPU Slave Interface Operating Timing**

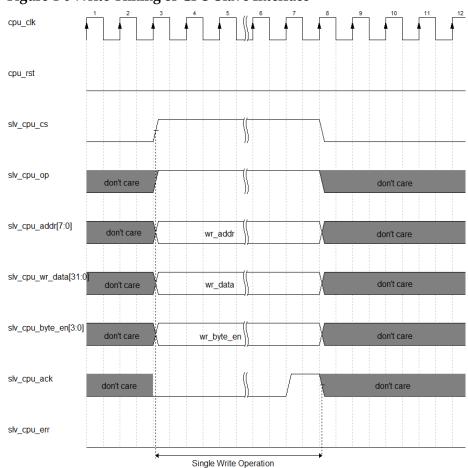

Write operating of CPU Slave Interface

When users need to write the register through the CPU Slave Interface, slv\_cpu\_cs needs to be pulled up to select the Interface, and slv\_cpu\_op also needs to be pulled up to indicate the write operation. Users send register address, write data, and enable byte through slv\_cpu\_addr, slv\_cpu\_wr\_data, and slv\_cpu\_byte\_en signals. When IP completes this write operation, the slv\_cpu\_ack signal is pulled up. Slv\_cpu\_cs, slv\_cpu\_op, slv\_cpu\_addr, slv\_cpu\_wr\_data and slv\_cpu\_byte\_en signals need to remain unchanged until slv\_cpu\_ack signal is pulled up. The write timing of CPU Slave Interface is as shown in Figure 4-6.

Figure 4-6 Write Timing of CPU Slave Interface

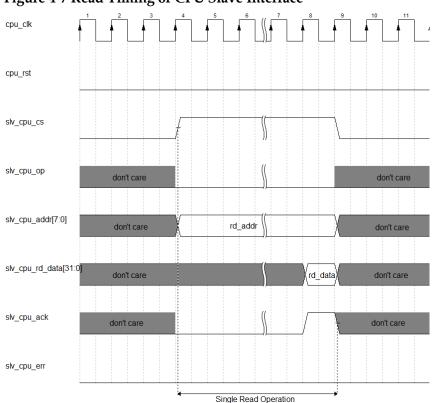

Read operating of CPU Slave Interface

When users need to read the register through the CPU Slave Interface, slv\_cpu\_cs should be pulled up to select the Interface and slv\_cpu\_op should be pulled down to indicate the read operation. Users send the register address through the slv\_cpu\_addr signal. When the IP completes the read operation, the slv\_cpu\_ack signal is pulled up and the read data is in slv\_cpu\_rd\_data. Slv\_cpu\_cs, slv\_cpu\_op, slv\_cpu\_addr signals need to remain unchanged until slv\_cpu\_ack signal is pulled up. When the CPU Slave Interface executes read operation, IP will return 4 bytes of read data. The read timing of CPU Slave Interface is as shown in Figure 4-7.

Figure 4-7 Read Timing of CPU Slave Interface

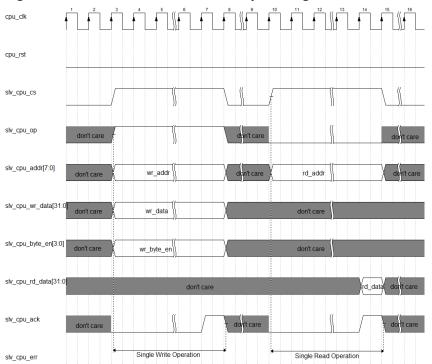

The read and write operating alternatively of CPU Slave Interface The read and write operating alternatively timing of CPU Slave Interface are as shown in Figure 4-8.

Figure 4-8 Read and Write Alternatively Timing of CPU Slave Interface

#### 4.11.2 SDIO CMD52 Interface

When Host accesses CIS or Function1 registers through CMD52, the user needs to send and receive data through SDIO CMD53 interface. After IP receives CMD52 accessing CIS or Function1 register, the Interface of SDIO CMD52 generates the corresponding data request, and the user shall respond according to the corresponding timing.

#### Write Operating of SDIO CMD52 Interface (RAW flag = 1)

When Host executes write operation through CMD52, users need to return the current value of the register after completing the register write operation.

When IP receives a correct CMD52 write operation and the register address is Function1, IP generates a write data request on SDIO CMD52 Interface. At this time, IP pulls up sdio\_cmd52\_cs signal, indicating that the SDIO CMD52 Interface has a data request. At the same time, sdio\_cmd52\_r\_w and sdio\_cmd52\_raw signals are pulled up, indicating that it is the write operation of RAW flag = 1. When sdio\_cmd52\_cs = 1, sdio\_cmd52\_fn\_num, sdio\_cmd52\_addr, sdio\_cmd52\_wr\_data signal are valid. After the user completes the write operation, it is required to pull up sdio\_cmd52\_ack one cycle to inform IP that the write operation is completed. When IP detects that sdio\_cmd52\_ack is 1, R5 is automatically sent to Host.

The write operation is executed when RAW flag = 1.Users need to return the current value of the write register in sdio\_cmd52\_rd\_data while pulling up sdio\_cmd52\_rd\_ack, which will return to the Host in the Read or Write Data field of R5.

The write timing of SDIO CMD52 Interface (RAW flag = 1) is as shown in Figure 4-9.

Figure 4-9 Write Timing of SDIO CMD52 Interface (RAW flag = 1)

#### Write Operating of SDIO CMD52 Interface (RAW flag = 0)

When Host executes write operation through CMD52 and RAW flag is 0. the user does not need to return the current value of the register after completing the register write operation.

When IP receives a correct CMD52 write operation and the register address is Function1, IP generates a write data request on SDIO CMD52 Interface. At this time, IP pulls up sdio cmd52 cs signal, indicating that the SDIO CMD52 Interface has a data request. At the same time, sdio\_cmd52\_r\_w signal is pulled up and sdio\_cmd52\_raw signal is pulled down, indicating that it is the write operation of RAW flag = 0. When sdio\_cmd52\_cs = 1, sdio\_cmd52\_fn\_num, sdio\_cmd52\_addr, sdio cmd52 wr data signal are valid. After users completes the write operation, it is required to pull up sdio\_cmd52\_ack one cycle to inform IP that the write operation is completed. When IP detects that sdio cmd52 ack is 1, R5 is automatically sent to Host.

The write operation is executed when RAW flag = 0. Users do not need to return the current value of the write register in sdio\_cmd52\_rd\_data while pulling up sdio\_cmd52\_ack. IP will automatically put the field value of CMD52 Write Data in Read or Write Data field of R5, returning to Host.

The write timing of SDIO CMD52 Interface (RAW flag = 0) is as shown in Figure 4-10.

Figure 4-10 Write Timing of SDIO CMD52 Interface (RAW flag = 0)

#### SDIO CMD52 Interface Read Operating

When Host executes read operation through CMD52, the user returns the register value after receiving the read request.

When IP receives a correct CMD52 write operation and the register address is Function1, IP generates a write data request on SDIO CMD52 Interface. At this time, IP pulls up sdio\_cmd52\_cs signal, indicating that the SDIO CMD52 Interface has a data request. At the same time, sdio\_cmd52\_r\_w signal is pulled up, indicating that it is the read operaiton. When sdio\_cmd52\_cs = 1, sdio\_cmd52\_fn\_num and sdio\_cmd52\_addr signal are valid. After the user completes the read operation, it is required to pull up sdio\_cmd52\_ ack one cycle to inform IP that the read operation is

to pull up sdio\_cmd52\_ack one cycle to inform IP that the read operation is completed. When IP detects that sdio\_cmd52\_ack is 1, R5 is automatically sent to Host.

Since it is a read operation, the user needs to return the read register value in sdio\_cmd52\_rd\_data while pulling up sdio\_cmd52\_rd\_ack. The value will return to the Host in the Read or Write Data field of R5.

The read operation timing of SDIO CMD52 Interface is as shown in Figure 4-11.

Figure 4-11 Read Timing of SDIO CMD52 Interface

#### CMD52 Timeout

According to the SDIO standard, the delay range of NCR from the last bit of Command to the first bit of Response is 2~64 clock cycles. Therefore, the user should not have more than 50 clock cycles interval between valid sdio cmd52 cs and valid sdio cmd52 ack (Due to sampling delays within IP). In 50 clock cycles after sdio\_cmd52\_cs is valid, if the user can not return to sdio\_cmd52\_ack, please give up this CMD52 operation, and sdio cmd52 ack does not to pull up again. The Host considers this operation times out.

#### 4.11.3 SDIO CMD53 Interface

When Host reads and writes CIS or Function1 registers through CMD53, the user need to control data transfer through SDIO CMD53 Interface. After IP receives CMD53 of reading and writing CIS or Function1 register, the interface of SDIO CMD53 generates the corresponding data request, and the user shall respond according to the corresponding timing.

The SDIO CMD53 command includes Bytes Transfer mode and Block Transfer mode. When CMD53 is in Bytes Transfer mode, SDIO CMD53 Interface generates a read-write operation, and the length is CMD53 Byte/Block Count field. When CMD53 is in Block Transfer mode, SDIO CMD53 Interface generates N times of read and write, N is CMD53 Byte/Block Count field, and the length is corresponding Function Block Size. Therefore, the user cannot perceive whether the operation is Bytes Transfer or Block Transfer. He only needs to transfer data in accordance with the corresponding timing.

#### SDIO CMD53 Interface Write Operation

Each write request represents a Bytes Transfer write or a single Block write in a Block Transfer.

When IP receives a correct CMD53 write operation and the register address is Function1, IP automatically responds to R5. The write data request is then generated on the SDIO CMD53 Interface. IP pulls up sdio\_cmd52\_cs signal, indicating there is a write data request on SDIO CMD53 Interface. When sdio\_cmd52\_cs = 1, sdio\_cmd53\_fn\_num, sdio\_cmd53\_addr, sdio\_cmd53\_len, sdio\_cmd53\_op\_code signals are valid.

When Host writes data to IP through sdio\_dat, users can receive the write data through sdio\_cmd53\_wr\_valid and sdio\_cmd53\_wr\_data. The number of write bytes at one time is equal to the value of sdio\_cmd53\_len. IP automatically verifies the correctness of CRC16 and End bit.

When Host completes a write operation in Bytes Transfer or a single Block write operation in Block Transfer, and IP has sent CRC status and End bit to Host, sdio\_cmd53\_wr\_end is pulled up to inform the user that the write operation is completed. Sdio\_cmd53\_wr\_ok is used to indicate whether the write data is correct or not. sdio\_cmd53\_wr\_ok synchronizes with sdio\_cmd53\_wr\_end. When sdio\_cmd53\_wr\_ok is 1, it means that the write operation is correct and the user needs to process the data of the write operation. When sdio\_cmd53\_wr\_ok is 0, it means that the write operation has CRC16 or End bit or CRC status sending error, and the user needs to abandon the data of the write operation.

In Block Transfer, if IP receives a Block write operation with an error, IP will abandon the subsequent data reception.

When user detects sdio\_cmd53\_wr\_end = 1, he needs to inform IP whether there is an idle buffer to continue receiving the subsequent data through sdio\_buffer\_full. If the user's buffer is full and cannot continue to receive data, sdio\_buffer\_full needs to be pulled up immediately after sdio\_cmd53\_wr\_end = 1 is detected. When the user pulls up sdio\_buffer\_full, IP will pull down sdio\_dat0 to the card busy state, until the user pulls down sdio\_buffer\_full. When Host detects that sdio\_dat0 is 0, the next write will not continue until it detects that sdio\_dat0 is pulled up.

The write operation timing of SDIO CMD53 Interface in the 4-bit mode is shown in Figure 4-12.

The write timing of SDIO CMD53 Interface in the 1-bit mode is shown in Figure 4-13.

Figure 4-13 The Write Timing of SDIO CMD53 Interface in the 1-bit Mode

#### SDIO CMD53 Interface Read Operating

Each read operation request means a read operation in Bytes Transfer or a single Block read in Block Transfer.

When IP receives a correct CMD53 read operation and the register address is Function1, IP automatically responds to R5. The read data request is then generated on the SDIO CMD53 Interface. IP pulls up sdio\_cmd53\_rd\_en signal, indicating there is a read data request on the SDIO CMD53 Interface. When sdio\_cmd52\_cs = 1, sdio\_cmd53\_fn\_num, sdio\_cmd53\_addr, sdio\_cmd53\_len, sdio\_cmd53\_op\_code signals are valid.

When the user receives the CMD53 read request, the user can send

the read data through sdio\_cmd53\_rd\_valid, sdio\_cmd53\_rd\_data and sdio\_cmd53\_rd\_ready. The sdio\_cmd53\_rd\_ready signal is pulled up every time, indicating that IP receives a byte of read data, and the user needs to get the new data ready again in the sdio\_cmd53\_rd\_data signal. The number of read bytes is equal to the value of sdio\_cmd53\_len. The user needs to control the length of sdio\_cmd53\_rd\_valid according to the value of sdio\_cmd53\_len. After sending enough bytes, the user pulls down sdio\_cmd53\_rd\_valid. IP sends data to sdio\_dat based on the length of request data of Host. After sending data, IP will automatically send CRC16 field and End bit, and then IP will pull up sdio\_cmd53\_rd\_end signal one cycle to inform the user that the read operation is completed.

IP does not support Read Wait function.

The read operation timing of SDIO CMD53 Interface in the 4-bit mode is shown in Figure 4-14.

Figure 4-14 The Read Timing of SDIO CMD53 Interface in the 4-bit Mode

The read timing of SDIO CMD53 Interface in the 1-bit mode is shown in Figure 4-15.

Figure 4-15 The Read Timing of SDIO CMD53 Interface in the 1-bit Mode

#### Abort

When Host reads and writes data through CMD53 in Infinite Block Mode, the read and write can be interrupted by Abort sent by CMD52. When IP receives CMD52 Abort and is writing data, IP will pull up sdio\_cmd53\_wr\_abort one cycle to inform the user to abort the write. If the user detects sdio\_cmd53\_wr\_abort = 1 and does not detect sdio\_cmd53\_wr\_end = 1 before, then this abort triggers a Bad abort and IP will receive abort before CRC status and End bit are sent. IP no longer generates sdio\_cmd53\_wr\_end = 1. The user needs to end the write operation and abandon the write data, as shown in Figure 4-16.

If the user receives both sdio\_cmd53\_wr\_abort = 1 and sdio\_cmd53\_wr\_end = 1, this abort triggers a good abort, which IP receives when it sends CRC status and End bit. The user needs to receive the write data, as shown in Figure 4-17.

If the user receives sdio\_cmd53\_wr\_abort = 1 after sdio\_cmd53\_wr\_end = 1, it indicates that abort is triggered in the card busy state, which means IP receives abort after CRC status and End bit sent, and it is a good abort. The user needs to receive the write data, as shown in Figure 4-18.

When IP receives CMD52 Abort and is reading data, IP will pull up sdio\_cmd53\_rd\_abort one cycle to inform the user to abort the read. If the user detects sdio\_cmd53\_rd\_abort = 1 and does not detect sdio\_cmd53\_rd\_end = 1 before, then this abort triggers a Bad abort and IP will receive abort before CRC status and End bit are sent. IP no longer generates dio\_cmd53\_rd\_end = 1. The user needs to end the read operation, which is unsuccessful, as shown in Figure 4-19.

Figure 4-18 Write Good Abort Case2

If the user receives both sdio\_cmd53\_rd\_abort = 1 and sdio\_cmd53\_rd\_end = 1, this abort triggers a good abort, which IP receives when it sends CRC status and End bit., and the read operation is successful as shown in Figure 4-20.

If the user receives sdio\_cmd53\_rd\_abort = 1 after sdio\_cmd53\_rd\_end = 1, it indicates that abort is triggered between two reads. IP receives abort after CRC16 and End bit are sent, and it is a Good abort as shown in Figure 4-21.

### 4.11.4 SDIO Tuning Interface

CMD19 is supported when IP is configured to UHS-I Card. IP receives the correct CMD19 and responds to R1 automatically. After R1 is sent, user sends Tuning Block Pattern through the SDIO Tuning Interface. Please see Figure 4-5 for Tuning Block Pattern The timing of SDIO Tuning Interface is shown in Figure 4-22.

## **5**<sub>Port List</sub>

The IO ports of Gowin SDIO Slave Controller IP are shown in Table 5-1.

| Table 5-1 IO Ports of Gowin SDIO Slave Controller IP |

|------------------------------------------------------|

|------------------------------------------------------|

| Signal         | I/O    | Bit Width | Description                                                                                                                                             |  |

|----------------|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SDIO Interface |        |           |                                                                                                                                                         |  |

| sdio_clk       | input  | 1         | SDIO clock input                                                                                                                                        |  |

| sdio_cmd_in    | input  | 1         | SDIO Command/Response input                                                                                                                             |  |

| sdio_cmd_out   | output | 1         | SDIO Command/Response output                                                                                                                            |  |

| sdio_cmd_oen   | output | 1         | SDIO Command/Response output enable, active-low                                                                                                         |  |

| sdio_dat0_in   | input  | 1         | The SDIO 1-bit mode is input of dat signal and the SDIO 4-bit mode is input of dat0 signal                                                              |  |

| sdio_dat0_out  | output | 1         | The SDIO 1-bit mode is output of dat signal<br>and the SDIO 4-bit mode is output of dat0<br>signal                                                      |  |

| sdio_dat0_oen  | output | 1         | The SDIO 1-bit mode is output enable of dat signal and the SDIO 4-bit mode is output enable of dat0 signal                                              |  |

| sdio_dat1_in   | input  | 1         | The SDIO 1-bit mode is the input of interrupt<br>signal and the SDIO 4-bit mode is the input of<br>dat1 and interrupt multiplexed signal                |  |

| sdio_dat1_out  | output | 1         | The SDIO 1-bit mode is output of interrupt<br>signal and the SDIO 4-bit mode is output of<br>dat1 and interrupt multiplexed signal                      |  |

| sdio_dat1_oen  | output | 1         | The SDIO 1-bit mode is output enable of<br>interrupt signal and the SDIO 4-bit mode is<br>output enable of dat1 and interrupt multiplexed<br>signal     |  |

| sdio_dat2_in   | input  | 1         | The SDIO 1-bit mode is the input of Read Wait signal and the SDIO 4-bit mode is the input of dat2 and Read Wait multiplexed signal                      |  |

| sdio_dat2_out  | output | 1         | SDIO 1-bit mode is the output of Read Wait<br>signal and SDIO 4-bit mode is the output of<br>dat2 and Read Wait multiplexed signal                      |  |

| sdio_dat2_oen  | output | 1         | SDIO 1-bit mode is output enable of Read Wait<br>signal and SDIO 4-bit mode is output enable of<br>dat2 and Read Wait multiplexed signal,<br>active-low |  |

| Signal                                           | I/O    | Bit Width | Description                                                                                                                                                                                                                                                        |  |

|--------------------------------------------------|--------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| sdio_dat3_in                                     | input  | 1         | The SDIO 1-bit mode is not defined and the SDIO 4-bit mode is the input of dat0                                                                                                                                                                                    |  |

| sdio_dat3_out                                    | output | 1         | The SDIO 1-bit mode is not defined and the SDIO 4-bit mode is the output of dat0                                                                                                                                                                                   |  |

| sdio_dat3_oen                                    | output | 1         | The SDIO 1-bit mode is not defined the SDIO 4-bit mode is the output enable of dat3 signal                                                                                                                                                                         |  |

| Reset                                            |        |           |                                                                                                                                                                                                                                                                    |  |

| rstn                                             | input  | 1         | Global asynchronous reset, active-low                                                                                                                                                                                                                              |  |

| cmd52_rst                                        | output | 1         | When Host reset SDIO through cmd52, this signal is 1. Synchronize with sdio_clk                                                                                                                                                                                    |  |

| Function1 Enable/Rea                             | ady    |           |                                                                                                                                                                                                                                                                    |  |

| fun1_ioe                                         | output | 1         | Function1 enable signal, reflecting the value of CCCR IOE1 Synchronize with sdio_clk                                                                                                                                                                               |  |

| fun1_ior                                         | input  | 1         | Function1 is ready Corresponding to CCCR<br>IOR1 Reg0x3 bit1                                                                                                                                                                                                       |  |

| Function1 Interrupt                              | T      | 1         |                                                                                                                                                                                                                                                                    |  |

| fun1_interrupt                                   | input  | 1         | 0: Function1 without interrupt<br>1: Function1 with interrupt                                                                                                                                                                                                      |  |

| CPU Slave Interface (Synchronize with cpu_clk)   |        |           |                                                                                                                                                                                                                                                                    |  |

| cpu_clk                                          | input  | 1         | cpu interface clock input                                                                                                                                                                                                                                          |  |

| cpu_rst                                          | input  | 1         | CPU interface synchronous reset input signal and synchronize with cpu_clk, 1 valid                                                                                                                                                                                 |  |

| slv_cpu_cs                                       | input  | 1         | CPU interface chip selection signal, active-high                                                                                                                                                                                                                   |  |

| slv_cpu_op                                       | input  | 1         | CPU interface operation mode; 0: read operation; 1: write operation                                                                                                                                                                                                |  |

| slv_cpu_addr                                     | input  | 8         | cpu interface operation address                                                                                                                                                                                                                                    |  |

| slv_cpu_wr_data                                  | input  | 32        | cpu interface write data                                                                                                                                                                                                                                           |  |

| slv_cpu_byte_en                                  | input  | 4         | CPU interface write operation byte enable:1:<br>enable; 0: disable<br>bit3 corresponding to slv_cpu_wr_data[31:24];<br>bit2 corresponding to slv_cpu_wr_data[23:16];<br>bit1 coreesponding to slv_cpu_wr_data[15:8];<br>bit0 corresponding to slv_cpu_wr_data[7:0] |  |

| slv_cpu_rd_data                                  | output | 32        | cpu interface read data                                                                                                                                                                                                                                            |  |

| slv_cpu_ack                                      | output | 1         | CPU interface operation response, when this bit is 1, indicating the operation is completed                                                                                                                                                                        |  |

| slv_cpu_err                                      | output | 1         | CPU interface operation error indication Valid<br>when slv_cpu_ack is 1.<br>1: error operation; 0: correct operation.                                                                                                                                              |  |

| SDIO CMD52 Interface (Synchronize with sdio_clk) |        |           |                                                                                                                                                                                                                                                                    |  |

| sdio_cmd52_cs                                    | output | 1         | SDIO CMD52 command enable<br>0: disable; 1: enbale                                                                                                                                                                                                                 |  |

| sdio_cmd52_r_w                                   | output | 1         | SDIO CMD52 read and write operation,<br>corresponding to IO_RW_DIRECT Command<br>(CMD52) Command R/W flag field.<br>0: read operation; 1: write operation                                                                                                          |  |

| sdio_cmd52_fn_nu<br>m                            | output | 1         | SDIO CMD52 Function Number,<br>corresponding to IO_RW_DIRECT Command<br>(CMD52) Function Number field.<br>0: Function0; 1: Function1                                                                                                                               |  |

| Signal                  | I/O       | Bit Width    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

|-------------------------|-----------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| sdio_cmd52_raw          | output    | 1            | SDIO CMD52 RAW enable, corresponding to<br>IO_RW_DIRECT Command (CMD52)<br>Command RAW flag field.<br>0: disable RAW; 1: enble RAW                                                                                                                                                                                                                                                                                                                                                                                           |  |

| sdio_cmd52_addr         | output    | 17           | SDIO CMD52 operation address,<br>corresponding to IO_RW_DIRECT Command<br>(CMD52) Command Register Address field.                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| sdio_cmd52_wr_dat<br>a  | output    | 8            | SDIO CMD52 write data, corresponding to<br>IO_RW_DIRECT Command (CMD52)<br>Command Write Data field. It is valid When the<br>SDIO CMD52 interface is in write mode.                                                                                                                                                                                                                                                                                                                                                          |  |

| sdio_cmd52_rd_dat<br>a  | input     | 8            | The SDIO CMD52 reads data or RAW data,<br>corresponding to IO_RW_DIRECT Response<br>(R5) command Read Data field.<br>When the SDIO CMD52 interface is in read<br>mode, the user needs to return the value of the<br>read register.<br>When the SDIO CMD52 interface is in RAW<br>mode, the user needs to return the value of the<br>write register                                                                                                                                                                           |  |

| sdio_cmd52_ack          | input     | 1            | SDIO CMD52 ack signal. When the user pulls<br>up the ack signal a single cycle, IP considers<br>that the user has completed the CMD52<br>operation and starts sending R5.<br>When this operation is a read operation, the<br>user needs to return the value of the read<br>address register to IP in sdio_cmd52_rd_data<br>while pulling up the ack.<br>When this operation is RAW operation, the<br>user needs to return the value of the write<br>address register to IP in sdio_cmd52_rd_data<br>while pulling up the ack |  |

| SDIO CMD53 Interfac     | e (Synchr | onize with s | dio_clk)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| sdio_cmd53_wr_en        | output    | 1            | SDIO CMD53 write enable<br>0: disable; 1: enbale                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |