# Gowin YunYuan Software **User Guide**

SUG100-1.4E,11/15/2018

## Copyright©2018 Guangdong Gowin Semiconductor Corporation. All Rights Reserved.

No part of this document may be reproduced or transmitted in any form or by any denotes, electronic, mechanical, photocopying, recording or otherwise, without the prior written consent of GOWINSEMI.

#### Disclaimer

GOWINSEMI®, LittleBee®, Arora™, and the GOWINSEMI logos are trademarks of GOWINSEMI and are registered in China, the U.S. Patent and Trademark Office and other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders, as described at www.gowinsemi.com. GOWINSEMI assumes no liability and provides no warranty (either expressed or implied) and is not responsible for any damage incurred to your hardware, software, data, or property resulting from usage of the materials or intellectual property except as outlined in the GOWINSEMI Terms and Conditions of Sale. All information in this document should be treated as preliminary. GOWINSEMI may make changes to this document at any time without prior notice. Anyone relying on this documentation should contact GOWINSEMI for the current documentation and errata.

## **Revision History**

| Date       | Version | Description                                                                                                                                                                                              |

|------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09/06/2018 | 1.2E    | Initial version published.                                                                                                                                                                               |

| 11/06/2018 | 1.3E    | GW1NZ-1 and GW1NSR-2C supported.                                                                                                                                                                         |

| 11/15/2018 | 1.4E    | <ul> <li>GW1N-6ES, GW1N-9ES and GW1NR-9ES devices removed;</li> <li>GW1N-1-MBGA160 and GW1N-1-PBGA204 packages removed;</li> <li>Supports GW1NSR-2;</li> <li>GW2AR-18-eLQFP144 package added.</li> </ul> |

## **Contents**

| Contents                                     | i   |

|----------------------------------------------|-----|

| List of Figures                              | iv  |

| List of Tables                               | vii |

| 1 About This Guide                           | 1   |

| 1.1 Purpose                                  | 1   |

| 1.2 Supported Products                       | 1   |

| 1.3 Related Documents                        | 1   |

| 1.4 Abbreviations and Terminology            | 2   |

| 1.5 Support and Feedback                     | 2   |

| 2 General Description                        | 3   |

| 2.1 Introduction                             | 3   |

| 2.2 Supported Devices                        | 5   |

| 3 Installation                               | 8   |

| 3.1 Environment Requirement                  | 8   |

| 3.2 Software Download                        | 8   |

| 3.3 Software Installation                    | 8   |

| 3.4 Software License Configuration           | 10  |

| 3.5 SynplifyPro License Configuration        | 11  |

| 3.5.1 Node-Locked License                    | 11  |

| 3.5.2 Floating License                       | 12  |

| 3.6 Place and Layout License Configuration   | 15  |

| 3.7 Software License Configuration (Linux)   | 18  |

| 3.7.1 SynplifyPro License Configuration      | 18  |

| 3.7.2 Place and Layout License Configuration | 20  |

| 4 Gowin Software GUI                         | 21  |

| 4.1 Title Bar                                | 21  |

| 4.2 Menu                                     | 22  |

| 4.3 Tool Bar                                 | 23  |

| 4.4 Project Area (Design)                    | 23  |

|                                              |     |

|     | 4.5 Process Area (Process)                      | 23 |

|-----|-------------------------------------------------|----|

|     | 4.6 Source File Editing Area                    | 24 |

|     | 4.7 Information Output area                     | 24 |

| 5   | Operation                                       | 25 |

|     | 5.1 Create a New Project                        | 25 |

|     | 5.1.1 Create a RTL Project                      | 25 |

|     | 5.1.2 Create a Post-Synthesis Project           | 28 |

|     | 5.2 Open an Existing Project                    | 31 |

|     | 5.3 Edit a Project                              | 32 |

|     | 5.3.1 Modify Project Device                     | 33 |

|     | 5.3.2 Edit a Project File                       | 34 |

|     | 5.3.3 Modify Project Configuration              | 42 |

|     | 5.4 Manage a Project                            | 46 |

|     | 5.4.1 Design Summary                            | 47 |

|     | 5.4.2 User Constraints                          | 48 |

|     | 5.4.3 Synthesize (Synplify Pro)                 | 49 |

|     | 5.4.4 Place & Route                             | 50 |

|     | 5.4.5 Program Device                            | 51 |

|     | 5.5 Exit IDE                                    | 52 |

| 6   | Tools in YunYuan Software                       | 53 |

|     | 6.1 Synplify Pro                                | 53 |

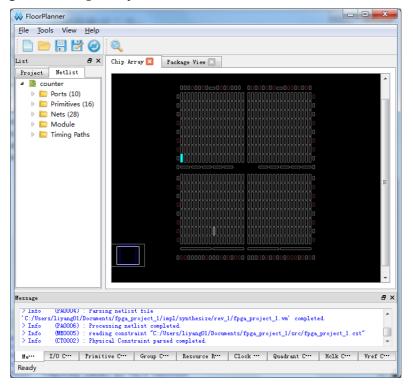

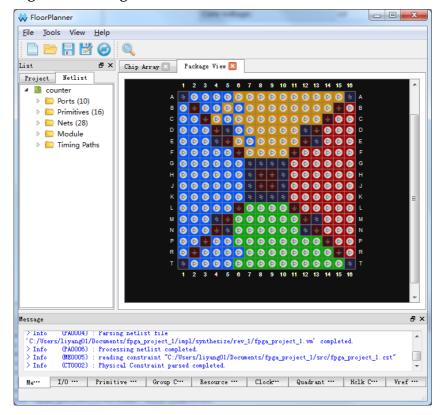

|     | 6.2 FloorPlanner                                | 53 |

|     | 6.3 Timing Constraints Editor                   | 55 |

|     | 6.4 Simulation                                  | 56 |

|     | 6.5 IP Core Generator                           | 56 |

|     | 6.6 Gowin Analyzer Oscilloscope                 | 59 |

|     | 6.7 Gowin Power Analyzer                        | 60 |

|     | 6.8 Memory Initialization File Editor           | 62 |

| 7   | Description of Gowin YunYuan Output Files       | 66 |

|     | 7.1 Place&Route Report                          | 66 |

|     | 7.2 Ports and Pins Report                       | 67 |

|     | 7.3 Timing Report                               |    |

|     | 7.4 Power Analysis Report                       |    |

| Α   | ppendix A SynplifyPro Attributes and Directives |    |

|     | A.1Attributes and Directives                    |    |

|     | A.2 Mapping Attributes and Directives           |    |

| Α   | ppendix B Command Line Options                  |    |

| - • | ·                                               |    |

| Appendix C Design Instance | 80 |

|----------------------------|----|

| C.1 Create a Project       | 82 |

| C.2 Implement a Project    | 82 |

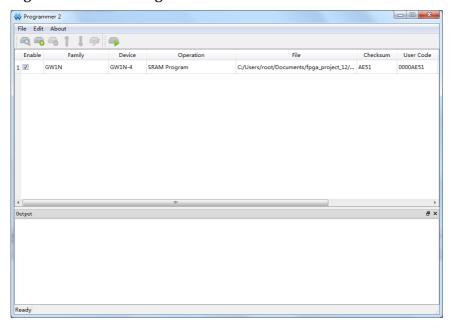

| C.3 Download Bitstream     | 83 |

SUG100-1.4E iii

## **List of Figures**

| Figure 2-1 GUI                                           | 4    |

|----------------------------------------------------------|------|

| Figure3-1 SynplifyPro Call Path                          | . 10 |

| Figure 3-2 Environment Variables Setting                 | . 12 |

| Figure 3-3 SCL Start GUI                                 | . 14 |

| Figure 3-4 SCL Configuration GUI                         | . 14 |

| Figure 3-5 SCL License Start                             | . 15 |

| Figure 3-6 Environment Variables Setting                 | .15  |

| Figure 3-7 License Error                                 | .16  |

| Figure 3-8 Manage License options                        | .16  |

| Figure 3-9 Gowin Floating License Server Start Interface | . 17 |

| Figure 3-10 Floating License Configuration Interface     | . 17 |

| Figure 3-11 Test Connection                              | . 18 |

| Figure 4-1 Gowin Software GUI                            | . 21 |

| Figure 4-2 File Changed                                  | 24   |

| Figure 5-1 Create a New Project                          | 26   |

| Figure 5-2 Create RTL Project Wizard                     | 26   |

| Figure 5-3 Select Device                                 | . 27 |

| Figure 5-4 Project Information Summary                   | 28   |

| Figure 5-5 Create a New Project                          | 28   |

| Figure 5-6 Create a Post-Synthesis Project               | 29   |

| Figure 5-7 Select Device                                 | 30   |

| Figure 5-8 Add Files                                     | 30   |

| Figure 5-9 Project Information Summary                   | . 31 |

| Figure 5-10Open an Existing Project                      | 32   |

| Figure 5-11 Open Project                                 | 32   |

| Figure 5-12 Project Design Area                          | . 33 |

| Figure 5-13 Project Device Information                   | 34   |

| Figure 5-14 Right-click Menu                             | 35   |

| Figure 5-15 Create a New File                            | 35   |

| Figure 5-16 Create a Verilog File                        | .36  |

| Figure 517 Create Config File                            | 36   |

| Figure 5-18 Config Files Setting                         | . 37 |

| Figure 5-19 Same Name Prompt                                                                                               | . 37                                 |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Figure 5-20 Constraints Files Existence                                                                                    | . 38                                 |

| Figure 5-21 Config Files Existence                                                                                         | . 38                                 |

| Figure 5-22 Right-click Actions in Design View                                                                             | . 39                                 |

| Figure 5-23 Copy File                                                                                                      | . 39                                 |

| Figure 5-24 Project Files Editing Actions                                                                                  | . 40                                 |

| Figure 5-25 External Editor                                                                                                | . 41                                 |

| Figure 5-26 Change Project File                                                                                            | . 41                                 |

| Figure 5-27 Save Project File                                                                                              | . 41                                 |

| Figure 5-28 Confirm File Deletion                                                                                          | . 42                                 |

| Figure 5-29Delete File Notice                                                                                              | . 42                                 |

| Figure 5-30Project Configuration View                                                                                      | . 42                                 |

| Figure 5-31 Reset                                                                                                          | . 43                                 |

| Figure 5-32 Place&Route Configuration                                                                                      | . 44                                 |

| Figure 5-33 Configure Multiplexing Pins                                                                                    | . 45                                 |

| Figure 5-34 Configure Bitstream File                                                                                       | . 45                                 |

| Figure 5-35 RTL Project Process Flow                                                                                       | . 47                                 |

| Figure 5-36 Project Summary                                                                                                | . 47                                 |

| Figure 5-37 Constraint File Prompt                                                                                         | . 48                                 |

| Figure 5-38 Warning-Creating a Constraints File                                                                            | . 48                                 |

| Figure 5-39 Timing Constraint File                                                                                         | . 49                                 |

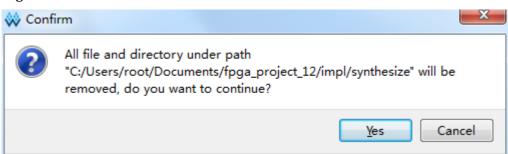

| Figure 5-40 "Clean" Confirm                                                                                                | . 50                                 |

| Figure 5-41 Gowin Programmer                                                                                               | . 52                                 |

| Figure 6-1 Chip Array View                                                                                                 | . 54                                 |

| Figure 6-2 Package View                                                                                                    | . 54                                 |

| Figure 6-3 Clock Creation Interface                                                                                        | . 55                                 |

| Figure 6-4 Start Simulation                                                                                                | . 56                                 |

| Figure 6-5 IP Core Generator Page                                                                                          | . 57                                 |

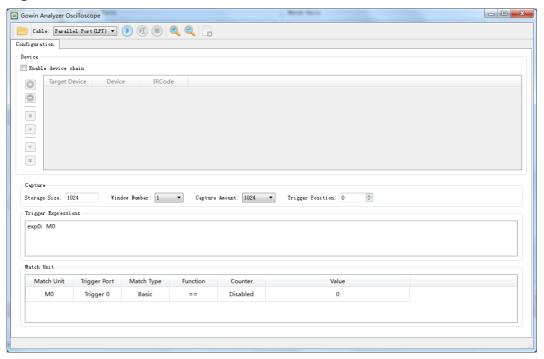

| Figure 6-6 GAO Configuration View                                                                                          | . 59                                 |

| Figure 6-7 GAO                                                                                                             | . 60                                 |

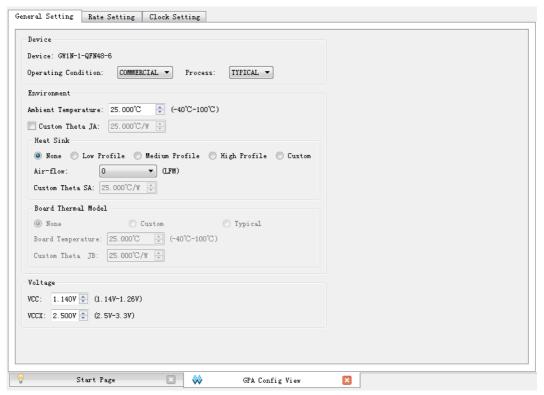

| Figure 6-8 GPA Config View                                                                                                 | . 61                                 |

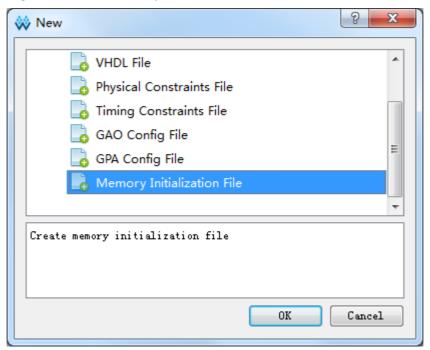

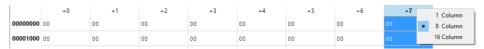

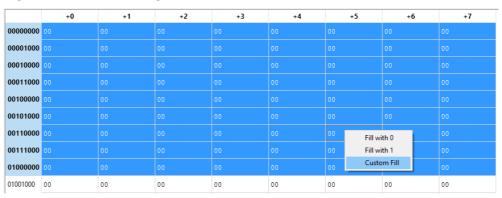

| Figure 6-9 New Memory Initialization File                                                                                  |                                      |

| ,                                                                                                                          | . 64                                 |

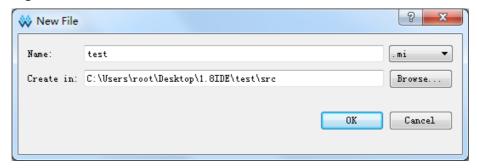

| Figure 6-10 New File                                                                                                       |                                      |

|                                                                                                                            | . 64                                 |

| Figure 6-10 New File                                                                                                       | . 64<br>. 65                         |

| Figure 6-10 New FileFigure 6-11 Initialization File Configuration                                                          | . 64<br>. 65<br>. 65                 |

| Figure 6-10 New File  Figure 6-11 Initialization File Configuration  Figure 6-12 Column Setting                            | . 64<br>. 65<br>. 65<br>. 65         |

| Figure 6-10 New File  Figure 6-11 Initialization File Configuration  Figure 6-12 Column Setting  Figure 6-13 Batch Setting | . 64<br>. 65<br>. 65<br>. 65         |

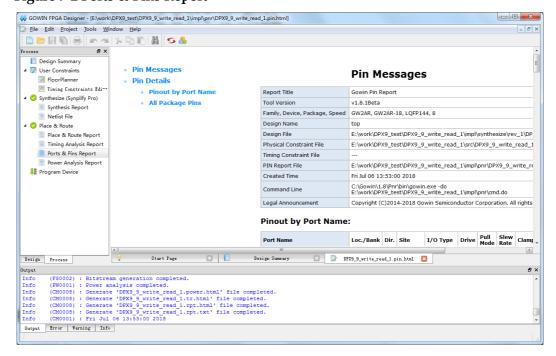

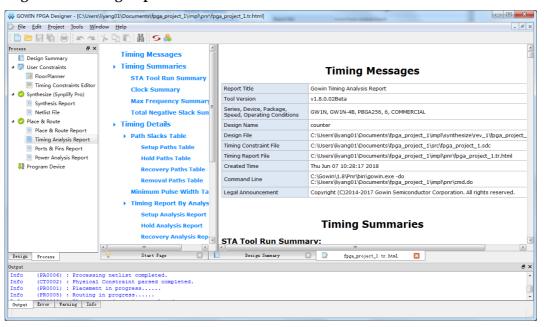

| Figure 6-10 New File                                                                                                       | . 64<br>. 65<br>. 65<br>. 65<br>. 67 |

| Figure C-1 Gowin YunYuan IDE   | 82 |

|--------------------------------|----|

| Figure C-2 Implement a Project | 82 |

| Figure C-3 Programmer          | 83 |

SUG100-1.4E vi

## **List of Tables**

| Table 1-1 Abbreviations and Terminology | 2 |

|-----------------------------------------|---|

|                                         |   |

| Table 2-1 Devices Supported             | 5 |

|                                         |   |

| Table 3-1 Components to Install         | 9 |

SUG100-1.4E vii

1About This Guide 1.1Purpose

# 1 About This Guide

## 1.1 Purpose

This manual predominantly documents Gowin software installation and operation and is designed to help users employ the software functionality to aid complex design. The software screenshots and the supported products listed in this manual are based on Windows 1.8.1Beta. As the software is subject to change without notice, some information may not remain relevant and may need to be adjusted according to the software that is in use.

## **1.2 Supported Products**

The information in this guide applies to the following products:

- GW1N series of FPGA products: GW1N-1, GW1N-2, GW1N-2B, GW1N-4, GW1N-4B, GW1N-6, GW1N-9;

- GW1NR series of FPGA products: GW1NR-4, GW1NR-4B, and GW1NR-9;

- GW1NS series of FPGA products: GW1NS-2, GW1NS-2C;

- GW2A series of FPGA products: GW2A-55 and GW2A-18;

- GW2AR series of FPGA products: GW2AR-18;

- GW1NZ series of FPGA products: GW1NZ-1;

- GW1NSR series of FPGA products: GW1NSR-2C and GW1NSR-2.

## 1.3 Related Documents

The latest user guides are available on GOWINSEMI Website. You can find the related documents at www.gowinsemi.com:

- 1. GW1N series of Products Data Sheet

- GW1NR series of FPGA Products Data Sheet

- 3. GW1NS series of FPGA Products Data Sheet

- 4. GW2A series of FPGA Products Data Sheet

- 5. GW2AR series of FPGA Products Data Sheet

SUG100-1.4E 1(83)

- GW1NZ series of FPGA Products Data Sheet

- 7. GW1NSR series of FPGA Products Data Sheet

- 8. Gowin Design Constraints Guide

- 9. Gowin FPGA Design Guide

- 10. Gowin Analyzer Oscilloscope User Guide

- 11. Gowin Power Analyzer User Guide

- 12. Gowin IP Core Generator User Guide

## 1.4 Abbreviations and Terminology

Table 1-1 shows the abbreviations and terminology used in this manual.

Table 1-1 Abbreviations and Terminology

| Abbreviations and Terminology | Name                               |

|-------------------------------|------------------------------------|

| CRC                           | Cyclic Redundancy Check            |

| CS                            | Wafer Level Chip Scale Package     |

| DLL                           | Delay-locked Loop                  |

| FPGA                          | Field Programmable Gate Array      |

| FF                            | Flip-Flop                          |

| IDE                           | Integrated Development Environment |

| IP Core                       | Intellectual Property Core         |

| LQ                            | Low-profile Quad Flat Package      |

| MAC                           | Media Access Control               |

| MG                            | Micro Ball Grid Array Package      |

| PC                            | Personal Computer                  |

| PLL                           | Phase-locked Loop                  |

| PG                            | Plastic Ball Grid Array            |

| QN                            | Quad Flat No-lead Package          |

| RTL                           | Register Transfer Level            |

| UG                            | Ultra Ball Grid Array Package      |

## 1.5 Support and Feedback

Gowin Semiconductor provides customers with comprehensive technical support. If you have any questions, comments, or suggestions, please feel free to contact us directly using the information provided below.

Website: <a href="www.gowinsemi.com">www.gowinsemi.com</a>

E-mail: <a href="mailto:support@gowinsemi.com">support@gowinsemi.com</a>

+Tel: +86 755 8262 0391

SUG100-1.4E 2(83)

2General Description 2.1Introduction

# 2 General Description

#### 2.1 Introduction

Gowin Yunnan Software is the new hardware development design environment for Gowin products. It supports generic hardware description language, and helps users to quickly implement code synthesis, manage placement and routing, generate and download bitstreams, etc. The Gowin Yunyuan Software also incorporates the IP Core Generator, which is dedigned to help developers quickly implement complex designs and the online debug tool, Gowin Analysis Oscilloscope, which can help users to efficiently identify and assess signal design issues.

To meet different user demands, Gowin YunYuan Software supports the creation of RTL and Post-Synthesis projects.

The input file for RTL project is the RTL file which contains hardware description language.

The input file for post-synthesis project is the netlist file, which is generated by user RTL synthesis.

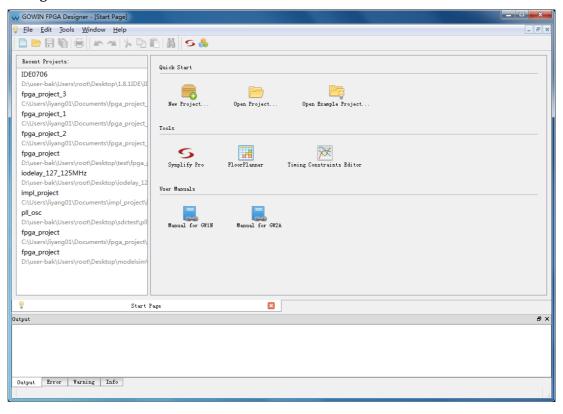

The Gowin YunYuan Software provides a GUI for both types of projects. Users can employ this software to quickly edit the constraints files, check the running results of SynplifyPro (RTL project only) and Place & Route, and start the GOWINSEMI FPGA download tool immediately to download the bitstream to the chip and implement the required functions. The interface of Gowin YunYuan Software is as shown in Figure 2-1.

SUG100-1.4E 3(83)

2General Description 2.1Introduction

Figure 2-1 GUI

SUG100-1.4E 4(83)

2General Description 2.2Supported Devices

## 2.2 Supported Devices

Table 2-1 lists the devices Gowin YunYuan software supports and the associated resources, packages, and speed.

**Table 2-1 Devices Supported**

| Device    | LUT4s | Flip-Flops | MULT18 x 18 | PLL | Package             | Speed |

|-----------|-------|------------|-------------|-----|---------------------|-------|

|           |       | 864        |             |     | WLCSP30             | 4/5/6 |

|           |       |            |             |     | QN32                |       |

|           |       |            | 0           | 1   | QFN48               |       |

| GW1N-1    | 1,152 |            |             |     | LQFN100             |       |

|           |       |            |             |     | LQFN144             |       |

|           |       |            |             |     | MBGA160             |       |

|           |       |            |             |     | PBGA204             |       |

|           |       |            |             |     | WLCSP72             |       |

|           |       |            |             |     | QFN32               |       |

|           |       |            |             |     | QFN88               |       |

|           |       |            |             |     | QFN48               |       |

| GW1N-2    | 2,304 | 1,728      | 16          | 2   | LQFP100             | 4/5/6 |

|           |       |            |             |     | LQFP144             |       |

|           |       |            |             |     | MBGA160             |       |

|           |       |            |             |     | PBGA256             | -     |

|           |       |            |             |     | PBGA256M<br>WLCSP72 |       |

|           |       |            |             |     | QFN32               | _     |

|           | 2,304 |            |             |     | QFN88               |       |

|           |       | 8 3,456    | 16          | 2   | QFN48               | 4/5/6 |

| GW1N-2B   |       |            |             |     | LQFP100             |       |

|           |       |            |             |     | LQFP144             |       |

|           | 4,608 |            |             |     | MBGA160             |       |

|           |       |            |             |     | PBGA256             |       |

|           |       |            |             |     | PBGA256M            |       |

|           |       |            |             |     | WLCSP72             |       |

|           |       |            |             |     | QFN32               |       |

|           |       |            |             |     | QFN88               |       |

| GW1N-4    |       |            |             |     | LQFP100             |       |

| OVV IIV-4 |       |            |             |     | LQFP144             |       |

|           |       |            |             |     | MBGA160             | -     |

|           |       |            |             |     | PBGA256             | -     |

|           |       |            |             |     | QFN48<br>PBGA256M   | _     |

|           |       |            |             |     | WLCSP72             |       |

|           | 4,608 |            |             | 2   | QFN32               | 4/5/6 |

| CMAN AD   |       |            |             |     | QFN88               |       |

| GW1N-4B   |       |            |             |     | LQFP100             |       |

|           |       |            |             |     | LQFP144             |       |

|           |       |            |             |     | MBGA160             |       |

SUG100-1.4E 5(83)

2General Description 2.2Supported Devices

| Device     | LUT4s | Flip-Flops | MULT18 x 18 | PLL | Package                      | Speed   |

|------------|-------|------------|-------------|-----|------------------------------|---------|

|            |       |            |             |     | PBGA256<br>QFN48<br>PBGA256M |         |

| 01444:     | 4000  | 0.450      | 40          |     | QFN88                        | 4.15.10 |

| GW1NR-4    | 4608  | 3456       | 16          | 2   | MBGA81                       | 4/5/6   |

| OWAND 4D   | 4000  | 0.450      | 40          | 0   | QFN88                        | 4/5/0   |

| GW1NR-4B   | 4608  | 3456       | 16          | 2   | MBGA81                       | 4/5/6   |

|            |       |            |             |     | LQFP144                      |         |

|            |       |            |             |     | UBGA332                      |         |

|            |       |            |             |     | PBGA256                      |         |

| 014/411 0  | 0040  | 5404       |             |     | LQFP100                      | 4/5/0   |

| GW1N-6     | 6912  | 5184       | 20          | 2   | QFN88                        | 4/5/6   |

|            |       |            |             |     | QFN48                        |         |

|            |       |            |             |     | LQFP176                      | -       |

|            |       |            |             |     | MBGA160<br>WLCSP64           | 1       |

|            |       |            |             |     | LQFP144                      |         |

|            |       |            |             |     | UBGA332                      |         |

|            |       |            |             |     | PBGA256<br>LQFP100           | _       |

| GW1N-6ES   | 6912  | 5184       | 20          | 2   | QFN88                        | 4/5/6   |

|            | 00.12 |            |             | _   | QFN48                        |         |

|            |       |            |             |     | LQFP176                      |         |

|            |       |            |             |     | MBGA160<br>WLCSP64           |         |

|            | 8640  | 6480       | 20          |     | LQFP144                      | 4/5/6   |

|            |       |            |             | 2   | UBGA332                      |         |

|            |       |            |             |     | PBGA256                      |         |

|            |       |            |             |     | LQFP100                      |         |

| GW1N-9     |       |            |             |     | QFN88                        |         |

|            |       |            |             |     | QFN48                        |         |

|            |       |            |             |     | LQFP176                      |         |

|            |       |            |             |     | MBGA160                      | _       |

|            |       |            |             |     | WLCSP64<br>LQFP144           |         |

|            |       |            | 20          |     | UBGA332                      | 4/5/6   |

|            |       |            |             |     | PBGA256                      |         |

| 014/41/050 | 00.40 | 0.400      |             |     | LQFP100                      |         |

| GW1N-9ES   | 8640  | 6480       |             | 2   | QFN88                        |         |

|            |       |            |             |     | QFN48<br>LQFP176             |         |

|            |       |            |             |     | MBGA160                      |         |

|            |       |            |             |     | WLCSP64                      |         |

| GW1NR-9    | 8640  | 6480       | 20          | 2   | LQFP144                      | 4/5/6   |

|            |       |            |             |     | QFN88                        |         |

| GW1NR-9ES  | 8640  | 6480       | 20          | 2   | LQFP144                      | 4/5/6   |

SUG100-1.4E 6(83)

2General Description 2.2Supported Devices

| Device    | LUT4s       | Flip-Flops | MULT18 x 18 | PLL | Package  | Speed |

|-----------|-------------|------------|-------------|-----|----------|-------|

|           |             |            |             |     | QFN88    |       |

|           |             |            |             |     | WLCSP36  |       |

|           |             |            |             |     | QFN32    |       |

| GW1NS-2   | 1728        | 1296       | 0           | 1   | QFN48    | 4/5/6 |

|           |             |            |             |     | LQFP144  |       |

|           |             |            |             |     | QFN32U   |       |

|           |             |            |             |     | WLCSP36  |       |

|           |             |            |             |     | QFN32    |       |

| GW1NS-2C  | 1728        | 1296       | 0           | 1   | QFN48    | 4/5/6 |

|           |             |            |             |     | LQFP144  |       |

|           |             |            |             |     | QFN32U   |       |

| GW1NZ-1   | 1152        | 864        | 0           | 1   | WLCSP16  | 4/5/6 |

| GW IIVZ-1 | 1102        | 004        | O           | '   | QFN32    |       |

| GW1NSR-2  | 1728        | 1080       | 0           | 1   | QFN48    | 4/5/6 |

| GW1NSR-2C | 1728        | 1080       | 0           | 1   | QFN48    | 4/5/6 |

|           | 20,736      | 15,552     | 48          | 4   | PBGA484  | 6/7/8 |

| GW2A-18   |             |            |             |     | PBGA256  |       |

|           |             |            |             |     | LQFP144  |       |

|           |             |            | 48          | 4   | QFN88    | 6/7/8 |

| GW2AR-18  | 20,736      | 15,552     |             |     | LQFP144  |       |

|           | ,           |            |             |     | LQFP176  |       |

|           |             |            |             |     | eLQFP144 |       |

| GW2A-55   | 54,720 41,0 | 41,040     | 40          | 6   | PBGA484  | 6/7/8 |

| GVV2A-33  | 34,720      | 71,040     | 40          | U   | PBGA1156 | 0/1/0 |

#### Note!

The supported devices may vary according to the software version in use. Please refer to the software you use for more detailed device information.

SUG100-1.4E 7(83)

# $\mathbf{3}_{\mathsf{Installation}}$

## 3.1 Environment Requirement

Windows: Win7/8/10(64bit), XP(32bit)

**Linux:** Centos6/7(64bit)、Red Hat 6/7(64bit)、SUSE 11/12(64bit)

Note!

YunYuan software does not currently support linux Centos5.

#### 3.2 Software Download

The Gowin YunYuan software installation packages consist of Windows and Linux versions. They are available for download on the Gowin Website:

- Installation package for Windows: Gowin Yunyuan for win(Vx.x.xbeta).exe, with the download link: http://www.gowinsemi.com/support/download\_eda/.

- Installation package for Linux is compressed with the name "Gowin Yunyuan for linux(Vx.x.xbeta).rar". The download link is <a href="http://www.gowinsemi.com/support/download\_eda/">http://www.gowinsemi.com/support/download\_eda/</a>.

#### Note!

- Users need to register and log on to the Gowin website before downloading the installation package;

- The "x" in the installation package name "Vx.x.xbeta" refers to the software version.

## 3.3 Software Installation

#### Note!

- You must close anti-virus programs, such as 360 or Kingsoft AntiVirus, etc. before installing Gowin YunYuan software'

- The installation path should not contain any Chinese characters or spaces.

- Before installing any new versions of the Gowin YunYuan software, old versions should be installed.

- Table 3-1 shows the product options for the installation of Gowin YunYuan for Windows.

SUG100-1.4E 8(83)

3.3Software Installation

**Table 3-1 Components to Install**

| Components              | Description                                                                                                     | Comments                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Gowin YunYuan<br>GUI    | Gowin YunYuan GUI                                                                                               | Installation directory of the corresponding executable file: \x.x\IDE\bin\gowin_ide.exe                                                                                                                                                                                                                                                                                               |

| Pnr tool                | Gowin place and routing tool, including software simulation library, IBS module, and software related documents | <ul> <li>Installation directory of the corresponding executable file for P&amp;R software:     \( \notin \text{x.x\Pnr\bin\gowin.exe}; \)</li> <li>Software simulation directory:     \( \notin \text{x.x\Pnr\lib}; \)</li> <li>IBS module directory:     \( \notin \text{x.x\Pnr\lib}; \)</li> <li>Software related documents directory: \( \notin \text{x.x\Pnr\doc}. \)</li> </ul> |

| Device<br>programmer    | Gowin devices download tool, including programmer user documents                                                | <ul> <li>Installation directory of the corresponding executable file: \x.x\Programmer\bin\programmer .exe;</li> <li>The corresponding documents directory: \x.x\Programmer\doc.</li> </ul>                                                                                                                                                                                            |

| SyplifyPro for<br>Gowin | Gowin synthesis tool, including user documents                                                                  | <ul> <li>Installation directory of the corresponding executable file: \x.x\SynplifyPro\bin\synplify_pro. exe;</li> <li>The corresponding documents directory: \x.x\SynplifyPro\doc.</li> </ul>                                                                                                                                                                                        |

| Floorplanner            | Gowin physical constraints editing tool                                                                         | Installation directory of the corresponding executable file: \x.x\Floorplan\bin\floorplan.exe                                                                                                                                                                                                                                                                                         |

#### Note!

"x.x" in the directory name in the above table refers to the software version.

#### Windows Installation

Refer to the steps below to install the Gowin Yunyuan software on Windows.

1. Double-click on the installer to launch the installation process. Follow the install wizard to complete the installation.

#### Note!

- In the process of installation, users can change the installation directory as required.

- After installation, the software shortcut will be created on PC desktop by default

SUG100-1.4E 9(83)

2. Double-click the shortcut " to open Gowin YunYuan software.

#### **Linux Installation**

After decompressing the files, run the following command with root authority to open the YunYuan software: path/x.x.xBeta/IDE/bin/gw\_ide.

#### Note!

"x" in the installation package name "x.x.xbeta" refers to the software version.

#### Note!

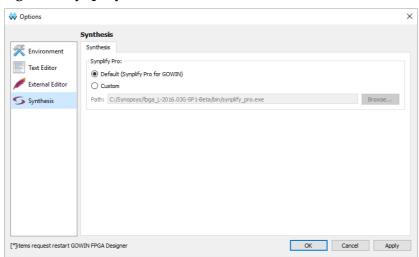

If you have previously installed Gowin Yunyuan software, ensure the installation directory of the new Gowin Yunyuan software is the same as the call path of SynplifyPro.

- Select "Tools > Options" from the menu bar;

- 2. Select the installation path for SynplifyPro, as shown in Figure 3-1.

Figure 3-1 Synplify Pro Call Path

## 3.4 Software License Configuration

After setting the "GOWIN\_HOME" environment variable, Gowin Yunyuan software licenses are required. Gowin Yunyuan software licenses include:

- SynplifyPro License;

- Place and Routing License;

Gowin YunYuan software licenses support node-locked license and floating license.

Users can apply for the required licenses on the Gowin website <a href="http://www.gowinsemi.com/support/license/">http://www.gowinsemi.com/support/license/</a>.

For license configuration, please refer to <u>3.5</u>SynplifyPro License Configuration and 3.6Place and Layout License Configuration.

SUG100-1.4E 10(83)

## 3.5 SynplifyPro License Configuration

#### 3.5.1 Node-Locked License

The node-locked license is based on PC MAC and is only suitable for the users of this PC. Please refer to the following steps after acquiring the SynplifyPro Node-Locked License:

#### Note!

If the other partner's tool was installed in the "C:\Synopsys\" directory, and there is the license file in this directory, conflict issues will occur when Gowin Synplify is searching a license. Because Synplify will search the license in this directory first by default, no matter the environment variables are configured or not.

Taking win7, 64-bit operating system for instance, please refer to the following steps to configure the environment variables.

Save license file

Save the license (licensefile.txt) to the target directory, for example, "E:\Synopsys\licensefile.txt".

- 2. Configure the license.

- a). Right-click on the "Computer" link, select "properties", and click the "Advanced system settings" to open the "System Properties" window;

- b). In the "System Properties" View, click "Advanced > Environment Variables>New" to open the "New User Variable", as shown in Figure 3-2. Enter the variable name and the value in the "New User Variable" dialog box.

Environment variable name:LM\_LICENSE\_FILE.

Variable value: License file location, such as "E:\Synopsys\licensefile.txt".

3. Click "OK".

SUG100-1.4E 11(83)

Figure 3-2 Environment Variables Setting

## 3.5.2 Floating License

When this configuration is employed, Gowin YunYuan is installed on your license server. Each PC in the LAN can use the floating license. Floating licenses have a user limit.

- First, start floating license using Synopsys Common Licensing (SCL) in the Yunyuan software installation package file "GowinLicenseServerForWindows\SCL".

- a). Click the "scl\_v2018.06\_windows.exe" SCL executable file to install the SCL software. Install it according to the wizard steps. Configure the "Site Information" as follows:

- "Site ID": The "siteid" value of the SynplifyPro License file (such as synp license.lic), such as 29247;

- "Site Administrator": The administrator name of this PC;

- "Contact Information": Optional, the contact information of the administrator:

- b). Select the installation path according to the wizard steps, such as "C:\Synopsys\SCL". Click "next" until the page of installation done appears. For example, the "Completing the SCL 2018.06 Setup Wizard" page appears. Click "Finish" to complete the SCL installation.

- Go to the "2018.06\win32\bin" folder in the SCL installation path, "C:\Synopsys\SCL \2018.06\win32\bin", for example. There are two ways to start teh floating license. Take Win7, 64 bits operating system for instance:

- Commands Mode

- a) Copy the floating license file (such as synp license lic) to the local

SUG100-1.4E 12(83)

SCL installation path;

b) Modify the PC name in the floating license file and check the MAC address:

for example:

for the "SERVER hostname1 F8BC12950972 27020" content in the license file:

- "hostname1" should be modified to the PC name;

- "F8BC12950972" is the PC MAC;

- "27020" is the port number, which should be modified per the PC installed SynplifyPro, such as "SERVER GaoYun-PC F8BC12950972 27020".

- Modify the snpsImd path in the floating license file.

On the basis of the "snpsImd.exe" path in SCL, modify this line "VENDOR snpsImd /path/to/snpsImd" in the license file to "VENDOR snpsImd

C:\Synopsys\SCL\2018.06\win32\bin\snpsImd.exe", for example;

- d) Open the cmd window and run the command to start the license service;

The command is "path\lmgrd.exe" –c "path\licensefile" –l "path\logfile" –z –s;

- e) After running, check the log file in the "path\logfile" directory to confirm that if the license has been installed successfully.

- SCL Configuration Mode

- a) Copy the floating license (such as synp\_license.lic) to the local SCL installation path;

- Modify the PC name in the floating license file and check the MAC address (Refer to Step b of the command mode);

- c) Modify the snpslmd path in the floating license file. Refer to Step c of the command mode;

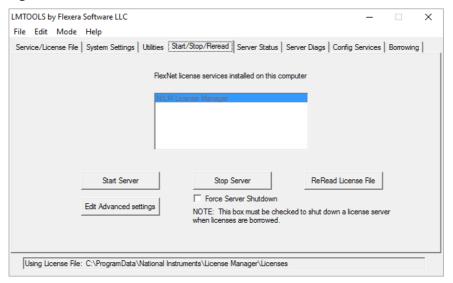

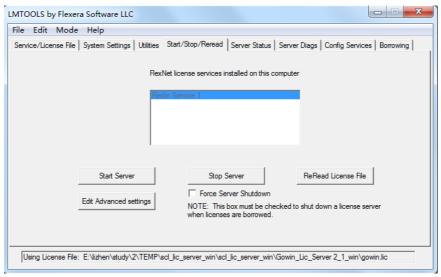

- d) Start "Imtools.exe" in snpsImd path; the GUI is as shown in Figure 3-3:

SUG100-1.4E 13(83)

Figure 3-3 SCL Start GUI

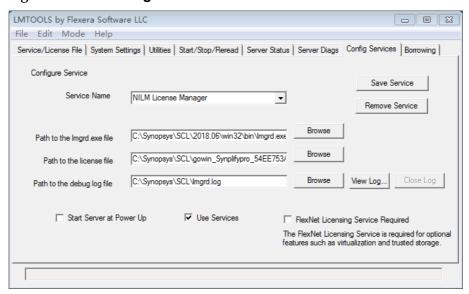

- e) See Figure 3-4, select "Config Services" to set the related files path;

- "Path to the Imgrd.exe file": Imgrd.exe file path;

- "Path to the license file": license file path;

- "Path to the debug log file": The path of the log file after license configuration. If there is no log file, you will need to create one before configuration.

Figure 3-4 SCL Configuration GUI

f) See Figure 3-5, start the license server after configuration. Select "Start/Stop/Reread", and then click "Start Server" to view the log file and verify that the server has started successfully.

SUG100-1.4E 14(83)

Figure 3-5 SCL License Start

#### Note!

After starting server license, the system environment variable "LM\_LICENSE\_FILE" is required to be configured before the configuration of the SynplifyPro floating license. As shown in Figure 3-6:

- Environment Variable name: LM\_LICENSE\_FILE;

- Environment Variable value: License files location, such as: 27020@192.168.31.33 and "192.168.31.33" is this PC IP address.

Figure 3-6 Environment Variables Setting

## 3.6 Place and Layout License Configuration

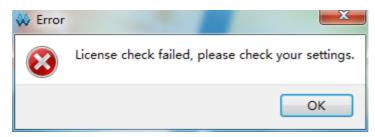

Gowin YunYuan software checks the license automatically when the user opens it. If the license is not correct, the software will not open, and an

SUG100-1.4E 15(83)

error message will be displayed, as shown in Figure 3-7.

Figure 3-7 License Error

Users can configure the license after the YunYuan software has been installed. See the steps as below:

- 1. Open the Gowin YunYuan software;

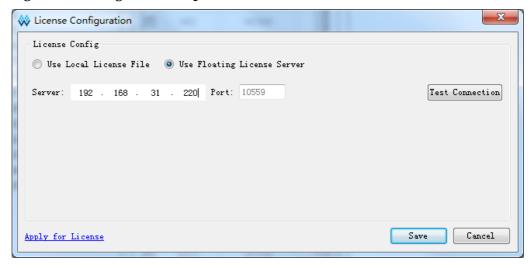

- 2. In the menu bar, click "Help> Manage License..." to open the "License Configuration", as shown in Figure 3-8.

Figure 3-8 Manage License options

- 3. User can choose local license file or floating license file.

- Use Local License File

Select "Browse..." to add the file path for node-locked License.

#### Note!

If there is no License file, apply the license by clicking "Apply for License" in the lower-left of the "License Configuration" View.

Use Floating License Server

First, start floating license using PnrLicenseServer in Yunyuan software installation package file

"GowinLicenseServerForWindows\PnrLicenseServer". There are two ways to start PnrLicenseServer:

a). Doubel click on "gwlic\_server.exe";Copy the floating license file (gowin license.lic, for example) to

SUG100-1.4E 16(83)

"GowinLicenseServerForWindows\PnrLicenseServer". Rename the floating license file as "gowin.lic". Double click "gwlic\_server.exe".

#### b). Commands Mode

- Copy the floating license file (gowin\_license.lic, for example) to "GowinLicenseServerForWindows\PnrLicenseServer". In the cmd window, execute the "gwlic\_server.exe –l license.txt" command in the directory of gwlic\_server.exe.

- Figure 3-9 shows the interface after the server has started.

Figure 3-9 Gowin Floating License Server Start Interface

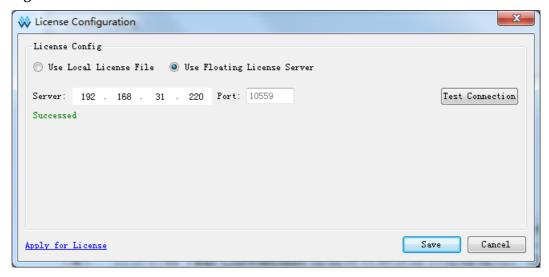

After successfully starting the server, input the server IP address in the "Licese Configuration" view, as shown in Figure 3-10.

Figure 3-10 Floating License Configuration Interface

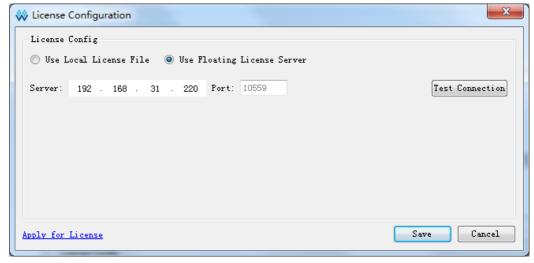

Click the "Licese Configuration" button on the right to test whether the connection has been successful. If successful, "Successed" will appear in the "License Configuration" view,

SUG100-1.4E 17(83)

#### as shown in Figure 3-11.

**Figure 3-11 Test Connection**

## 3.7 Software License Configuration (Linux)

### 3.7.1 SynplifyPro License Configuration

In the Linux version of the software, only floating licenses are available for SynplifyPro. Save the license.txt file to the Imgrd path. If it's saved to the other directory, absolute path needs to be used.

Take 64-bit Linux, Redhat 5, for instance, refer to the following steps to configure the license (only the floating license is supported):

- In the "GowinLicenseServerForLinux\SCL\SynopsysInstaller" folder, install "SynopsysInstaller" according to the installation notes described in "installer INSTALL README.txt":

- a). In the "SynopsysInstaller\_v4.1.run" file path, modify the file permission, right-click to open the command line, and run "chmod 755 SynopsysInstaller v4.1.run".

- b). Switch to "root", execute the installation command in the "SynopsysInstaller\_v4.1.run" path:

- "./SynopsysInstaller v4.1.run -d /usr/synopsys/installer".

- c). Exit "root". Make sure the installation path is available. Run the command as follows in the current path:

- "chmod -R 755 /usr/synopsys/installer".

- d). Add Environment Variables:

- If C shell is used, run the command as follows: "set path=(/usr/synopsys/installer \$path)"

- If Bourne or Bash shell is used, run the command as follows: "PATH=/usr/synopsys/installer:\$PATH""

SUG100-1.4E 18(83)

#### export PATH"

- e). Users can search the environment variables using the "export" command to confirm whether the path was added successfully.

- Install the SCL according to the notes described in "scl\_INSTALL\_README.txt" in the "GowinLicenseServerForLinux\SCL\doc" path. The installation path is "path/ scl\_lic\_server\_linux/v2018.06", for example.

- a). If it is the suse system, delete the "scl\_v2018.06\_linux64.spf" file in the "GowinLicenseServerForLinux\SCL" path. If it is the other systems, such as CentOS, Redhat, UBUNTU, etc, delete the "scl\_v2018.06\_suse64.spf" file.

- b). After the installation of SynopsysInstaller is done, install the SCL software, run the command as follows:

"installer -batch\_installer -source <SOURCE> -target <DEST>" <SOURCE> is the spf file path. <DEST> is the SCL installation path. During installation, a window will appear to ask if the files are all installed correctly. Click "yes" to continue the installation.

- 3. Confirm and modify the license file:

- a). Modify PC name and confirm MAC address.

In the floating license file, modify "hostname1" in "SERVER hostname1 000C293B1A2B 27020" to the PC name.

"000C293B1A2B" is "HWaddr", and "27020" is the port number. Modify the license according to the PC on which SynplifyPro is installed, such as: "SERVER gaoyun 000C293B1A2B 27020".

- b). Modify snpsImd path. On the basis of the "snpsImd.exe" path in SCL, modify this line "VENDOR snpsImd /path/to/snpsImd" in the license file to the local snpsImd path; for example: "VENDOR snpsImd path/scl\_lic\_server\_linux/v2018.06/linux64/bin/snpsImd".

- Configure the License using SCL

In the Imgrd path, execute the "./Imgrd -c license.txt -l lic.log" command to generate the log file "lic.log". View the lic.log to verify whether the configuration has been successful;

- 5. Configure the Environment Variable:

- a) Configure the "LM\_LICENSE\_FILE" environment variable. The value format should be "Port number @ Host name", for example: setenv LM\_LICENSE\_FILE\_27020@gaoyun

- b) The default port number is 27020 during License installation. It can be modified by finding the character string "27020" in the license file and replacing this string with the designated port.

#### Note!

All the commands should be executed in the path of the license installation directory. Furhter license commands are as follows:

• Configure license——"./lmgrd –c licensefile –l lic.log";

SUG100-1.4E 19(83)

- Stop license——"./Imdown -c licensefile";

- Check license status——"./lmstat -a -c port number@ host name".

## 3.7.2 Place and Layout License Configuration

In Linux, the Gowin License configuration is the same as that of Windows, please refer to <u>3.6Place and Layout License Configuration</u>.

SUG100-1.4E 20(83)

4Gowin Software GUI 4.1Title Bar

## 4Gowin Software GUI

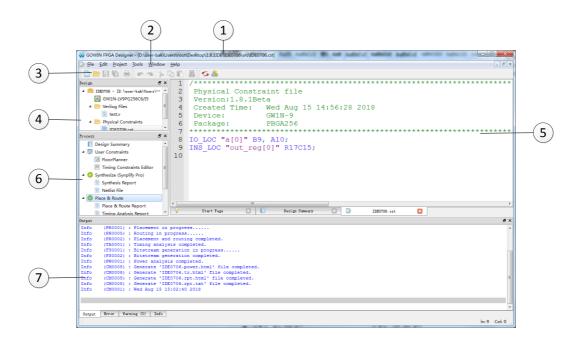

Figure 4-1 shows the YunYuan software GUI. It consists of the title bar, menu bar, tool bar, project area (Design View), process area (Process View), source file editing area, and information output area (Output).

Figure 4-1 Gowin Software GUI

- ① Title Bar

- 3 Tool Bar5 Source File Editing

- Area

7 Information Output area

- 2 Menu

- 4 Project Area

- 6 Process Area

## 4.1 Title Bar

Title bar shows the current project path, name, and the name of the file that is currently open.

SUG100-1.4E 21(83)

4Gowin Software GUI 4.2Menu

#### 4.2 Menu

The menu bar contains links to the tools and functionality that are commonly used in projects, including the File, Edit, Project, Tools, Window, and Help options. See the following for details:

#### 1. File:

- New: Used to create a new file and project;

- Open: Used to open a new file and project;

- Save: Used to "save" or "save as" the project files;

- Close: Used to close project, project files, and page;

- Print: Print;

- Recent Files: Shows the files that were recently open. The user can click on the names of these files to reopen them;

- Recent Projects: Shows the names of the projects that were recently open. The user can click on the names of these projects to reopen them;

- Exit: Used to exit and close the Gowin YunYuan software.

#### 2. Edit:

- Undo: Used to undo your last operation;

- Redo: Used to redo the last operation;

- Cut: Used to cut the characters;

- Copy: Used to copy the characters;

- Paste: Used to paste the characters;

- Select All

- Find: Used to find or change key words;

- Macros

#### 3. Project

- New File: Used to create a new file;

- Add File: Used to add a file;

- Clean: Used to clean all the generated files and file folders in the impl folder after running the project;

- Set Device: Used to change the project device, package, and speed;

- Configuration: Configuration for running the project;

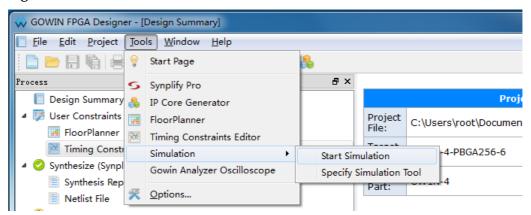

#### 4. Tools

- Start Page

- Synplify Pro: Front-end integration software;

- Simulation

SUG100-1.4E 22(83)

4Gowin Software GUI 4.3Tool Bar

- IP Core Generator

- FloorPlanner: Physical constraints editor;

- Timing Constraints Editor;

- Gowin Analyzer Oscilloscope;

- Options: Used to open the required tools or set IDE parameters.

#### 5. Window

- Full Screen;

- Tile:

- Cascade:

- Reset Layout: Restores initial settings;

- Panels: Used to select whether to display GUI models or not;

- Start Page;

- Design Summary.

#### 6. Help:

- Contact Us: Click to contact us:

- Manage License;

- About: Shows software version and copyright information.

#### Note!

"Project" shows in the menu bar only after you create a new project.

### 4.3 Tool Bar

The Tool bar contains quick access buttons. These are as follows (from left to right): New File or Project, Open File or Project, Save, Save All, Print, Undo, Redo, Cut, Copy, Paste, and Find.

## 4.4 Project Area (Design)

The project area shows projects and the related files. Users can check or change the project device information, user design files, user constraints files, configuration files, etc.

## 4.5 Process Area (Process)

The process area provides FPGA design flow, including synthesis, place & route, and download bitstream files (program device). Users can also double click timing constraints editor and physical constraints editor to edit the constraints files.

SUG100-1.4E 23(83)

## 4.6 Source File Editing Area

Users can view and edit source files in the source file editing area.

The source file editing area shows different files, including new files or opened files, the generated files after synthesis or Place & Route, the "Start Page" and "Design Summary".

If the file currently displayed is modified, the term "File Changed" will appear in the file editing area, as shown in Figure 4-2. Select "Reload" to reload the file.

Figure 4-2 File Changed

To close the file currently displayed, click "File > Close", or click on the icon " that appears in the upper-right of the file editing area.

To close all the files in the file editing area, click "File > Close All".

## 4.7 Information Output area

The information output area displays the processing information when the software is running. Users can verify different outputs by manually switching between the tabs:

- Output: All information

- Error

- Warning

- Info: All other information

In the output tab, right-click and select "Clear" to clear all the information in the tab. Users can only clear the information that is displayed in the current tab if they right-click and select "Clear" in the Error tab, Warning tab, or Info tab.

If a Warning or an Error appears during running, the number of Warnings and Errors will be recorded and shown on each of the corresponding tabs.

SUG100-1.4E 24(83)

# **5**Operation

Gowin YunYuan is available in Windows and Linux. It supports GUI running mode and commands running mode. Take the GUI running mode in Windows for instance. Please refer to the following for the operation details.

For the command lines used for the commands mode, please refer to *Appendix B Command Line Options*.

## 5.1 Create a New Project

YunYuan software supports two kinds of projects: RTL and Post-Synthesis projects.

- 1. RTL projects employ user RTL design as input, and the entire flow includes synthesis, place&route, and downloading bitstream files.

- 2. Post-Synthesis projects use the synthesized logic netlist as input, so synthesis can be skipped, and place&route and download bitstream files can be implemented directly.

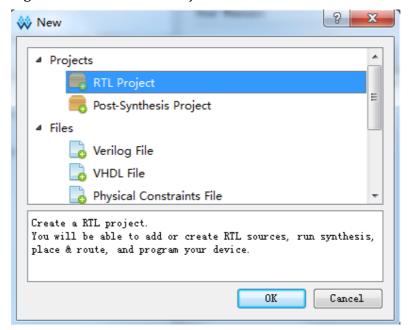

## 5.1.1 Create a RTL Project

1. From the File menu, choose "File> New..." to open the "New" dialog, as shown in Figure 5-1.

SUG100-1.4E 25(83)

5Operation 5.1Create a New Project

Figure 5-1 Create a New Project

#### Note!

There are different ways to open a "New" dialog:

- Using the "Ctrl+N" short cut;

- By clicking on the "New File or Project" icon that appears on the tool-bar;

- By selecting "Quick Start>New Project" on the Start Page.

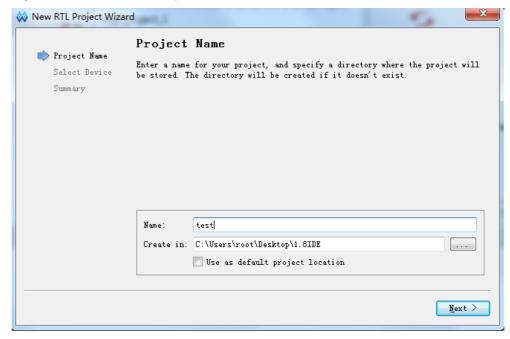

- 2. Select "RTL Project", and then click "OK" to open "New RTL Project Wizard", as shown in Figure 5-2.

Figure 5-2 Create RTL Project Wizard

3. Create the project "Name" and "Create in", as shown in Figure 5-2;

SUG100-1.4E 26(83)

- a). Enter the project name in the "Name" field;

- b). Click on the "...." icon to choose the project path.

#### Note!

- No Chinese characters or spaces can be included in the project path;

- The file path length is limited in both Windows and Linux. You cannot delete or copy the files with the length going over the limits;

- The path separator is "\" in Windows; for example, E:\Gowin\ide;

- If users select "Use as default project location", the project location will be set as the default location, and all later projects you create will be saved to this location.

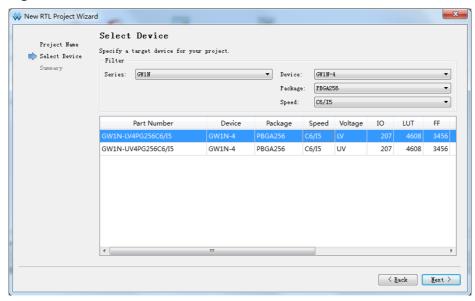

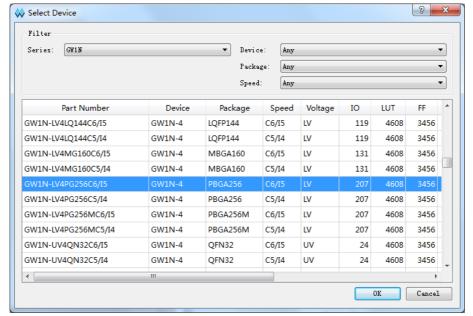

- Click "Next" to select the device, as shown in Figure 5-3:

- a). In this step, users can select the target device series, package, and speed.

- b). Choose package type from the "Package" drop-down list;

- c). Choose speed grade from the "Speed" drop-down list;

- d). Choose the detailed part number from the "Part Number" sub-window. It displays the detailed resource information related to the selected device.

Figure 5-3 Select Device

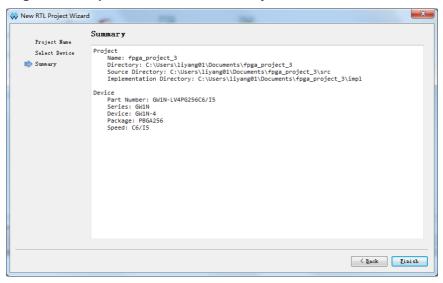

5. Click "Next" to open the Project Information Summary window, as shown in Figure 5-4.

SUG100-1.4E 27(83)

Figure 5-4 Project Information Summary

6. Click "Finish". The project now is created.

#### Note!

- The device can be changed after the project has been created. Please refer to 5.3Edit a Project>5.3.1Modify Project Device for further details.

- Users can add source files and constraints files after the project has been created. Please refer to 5.3Edit a Project>5.3.2Edit a Project File for the details.

## 5.1.2 Create a Post-Synthesis Project

1. From the File menu, choose "File> New..." to open the "New"dialog, as shown in Figure 5-5.

Figure 5-5 Create a New Project

#### Note!

There are different ways to open a "New" dialog:

SUG100-1.4E 28(83)

- Using the "Ctrl+N" short cut;

- Clicking on the "New File or Project" icon in the toolbar;

- By selecting "Quick Start>New Project" on the Start Page.

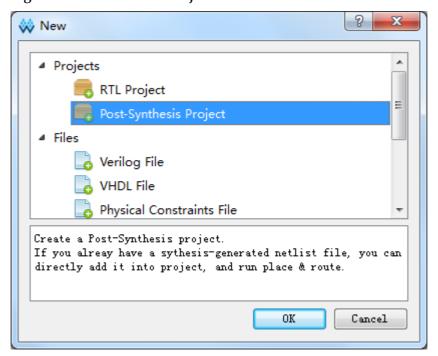

- 2. Select "Projects>Post-Synthesis Project", and then click "OK" to open "New Post-Synthesis Project Wizard", as shown in Figure 5-6.

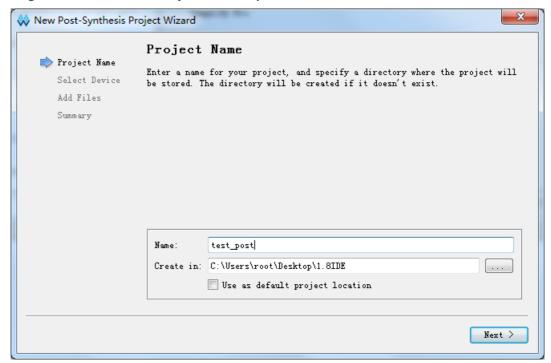

Figure 5-6 Create a Post-Synthesis Project

- 3. Create the project "Name" and "Create in", as shown in Figure 5-6;

- a). Enter the project name in the "Name" field;

- b). Click on the "icon to choose the project path.

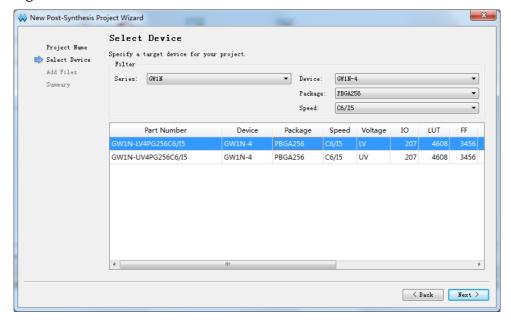

- 4. Click "Next" to select the device, as shown in Figure 5-7: In this step, users can select the target device series, package, and speed. Choose the detailed part number from the "Part Number" sub-window. It displays the detailed resource information related to the selected device.

SUG100-1.4E 29(83)

Figure 5-7 Select Device

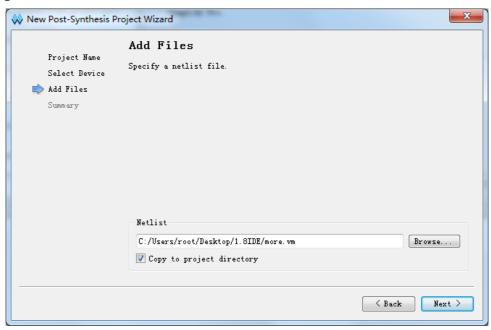

5. Click "Next" to add the Netlist files with the name suffix .v, .vm, .vo, .sv, .vma, and .vp, as shown in Figure 5-8.

#### Notel

If users select "Copy to project directory", the netlist files will be copied to the project location.

Figure 5-8 Add Files

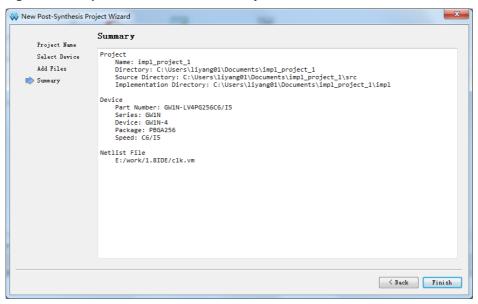

6. Click "Next" to open the Project Information Summary window, as shown in Figure 5-9. This includes the new post-synthesis project information, device information, and source files information.

SUG100-1.4E 30(83)

**Figure 5-9 Project Information Summary**

7. Click "Finish". The project now is created.

#### Note!

- The device can be changed after the project has been created. Please refer to 5.3Edit a Project>5.3.1Modify Project Device for further details.

- Users can add source files and constraints files after the project has been created. Please refer to 5.3Edit a Project>5.3.2Edit a Project File for the details.

# 5.2 Open an Existing Project

Use one of the following methods to open an existing project:

#### Method 1

1. From the File menu, select "File> Open ..." to open the "Open File" dialog box, as shown in Figure 5-10.

#### Note!

Users can also click on the " icon in the tool bar to open the "Open File" dialog box.

2. Choose the project file (\*.gprj) and click "Open" to open the existing project.

SUG100-1.4E 31(83)

⇔ Open File ▼ ⁴ゥ 搜索 test 组织 ▼ 新建文件夹 名称 修改日期 举刑 ☆ 收藏夹 ▶ 下载 configure 2017/6/22 14:24 文件本 📃 桌面 \mu impl 2017/6/22 14:24 文件本 ll src 2017/6/22 14:24 文件夹 💹 最近访问的位置 2017/6/22 14:43 test.gprj GPRJ 文件 1 KB test.gprj.user 2017/6/22 14:43 USER 文件 🃜 库 🔡 视频 ■ 图片 📔 文档 → 音乐 ■ 计算机 🌉 本地磁盘 (C:) 本地磁盘 (D:) □ 本地磁盘 (E:) 文件名(N): test.gpr All Files (\*) (\*.\*) 打开(O) **▼** 取消

Figure 5-10Open an Existing Project

#### Method 2

- 1. On the start page, click "bearing to open "Open Project" dialog box,

- 2. Choose the project file (\*.gprj) and click "Open" to open the existing project.

- 3. Click "Open" to open the project.

#### Method 3

From the File menu, click "File> Recent Projects", to open your required project.

#### Note!

- Users can also open recent projects from the projects list that is displayed on the left side of the start page.

- Recent Projects shows the recently opened projects. Users can click on the names of the files to re-open them;

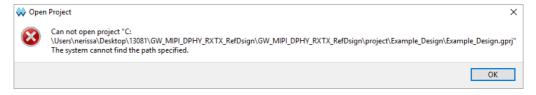

- If the project was deleted, the "Open Project" dialog box will appear, as shown in Figure 5-11.

### Figure 5-11 Open Project

#### Method 4

Find the project you established and find the \*.gprj file. Doule-click on the \*.gprj file to open the project with Gowin YunYuan software automatically.

# 5.3 Edit a Project

After creating or opening a project, users can edit the device information and the related files in the project design area, as shown in

SUG100-1.4E 32(83)

Figure 5-12.

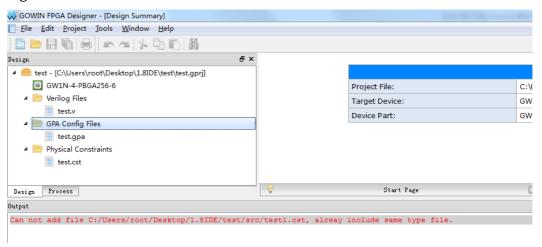

The Project Design Area contains the following:

- 1. The project path;

- 2. Chip info: Chip type, package type, and speed;

- 3. The current project files, including user design files, physical constraints files (.cst.), timing constraints files (.sdc), GAO config files (.gao), and GPA config files (.gpa), etc.

Figure 5-12 Project Design Area

# **5.3.1 Modify Project Device**

The second line in the project design area shows the device info. for the current project. Refer to the steps as below to modify the current project device.

- As shown in Figure 5-12, double-click "GW1N-LV4LQ144C5" to open the "Select Device" view, as shown in Figure 5-13;

- 2. In the "Select Device" view, select "Series" and "Device", select "Package" from the package drop-down list and select "Speed" from the speed drop-down list, and then select the detailed part number from the "Port Number" sub-window. Click "OK".

#### Note!

The "Port Number" sub-window displays the detailed resource information related to the selected device.

SUG100-1.4E 33(83)

Figure 5-13 Project Device Information

## 5.3.2 Edit a Project File

RTL projects need RTL design files (Source Files), constraints files, and configuration files. Constraints files contain the Physical Constraints File and Timing Constraints File; configuration files contain the GAO Config File and GPA Config File.

An RTL project can have multiple design files; however, only one physical constraints file and one timing constraints file can be active at a time.

The user netlist file is added to the Post-Synthesis project when it is created; as such, users only need to add the corresponding constraints files and configuration files after the project has been created.

Take an RTL project, for instance. Refer to the following sections to edit the project files.

- Create a New Project File

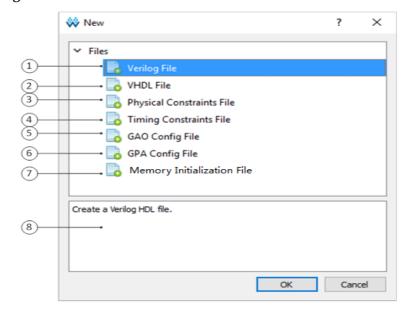

- a). As shown in Figure 5-14, right-click on a blank area of the project design area, select "New Files..." to open "New" dialog box, as shown in Figure 5-15;

- b). As shown in Figure 5-15, select the file type and click "OK" to create a new file.

SUG100-1.4E 34(83)

Figure 5-14 Right-click Menu

Figure 5-15 Create a New File

- Verilog File

- 3 Physical Constraints File

- ⑤ GAO Config File

- Memory Initialization File

- ② VHDL File

- 4 Timing Constraints File

- 6 GPA Config File

- (8) File Description

SUG100-1.4E 35(83)

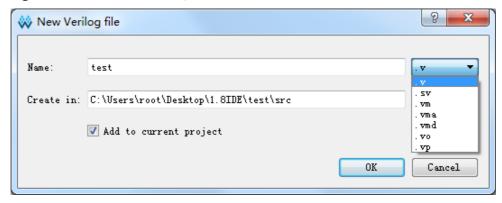

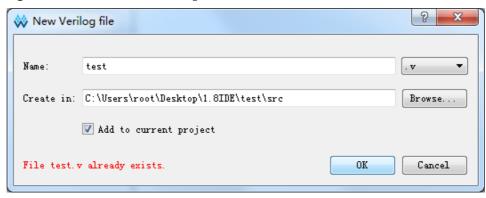

c). Take creating a Verilog File, for instance. Select "Verilog File" and click "OK" to open the Verilog File view, as shown in Figure 5-16.

Figure 5-16 Create a Verilog File

d). Enter the file name and click "OK".

#### Note!

- Users can select file extensions from the drop-down list. "Add to current project" is selected by default.

- User can open and edit the newly created blank file in the source file editing area.

- 2. Create a Configuration File

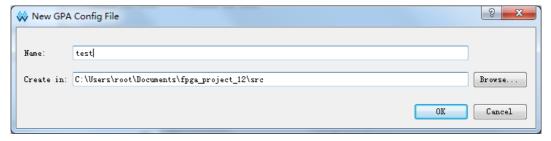

- a) As shown in Figure 5-14, right-click on a blank area of the project design area, select "New Files..." to open the "New" dialog box, as shown in Figure 5-15;

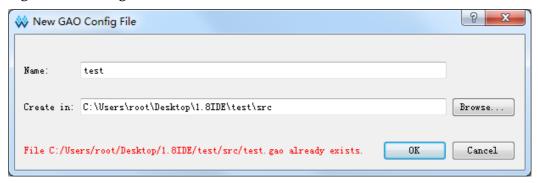

- b) As shown in Figure 5-15, select the file type and click "OK" to create a new file. Take creating a GPA Config File, for instance. Select "GPA Config File" and click "OK" to open the GPA Config File view, as shown in Figure 5-17.

- c) The newly created Config File will not be directly opened in the source file editing area directly. Users need to double-click the Config File in the project Design area to open and edit the blank Config File, as shown in Figure 5-18.

Figure 5--17 Create Config File

SUG100-1.4E 36(83)

Figure 5-18 Config Files Setting

#### Note!

- If the newly added Verilog File has the same name as an existing file, the same name prompt will appear, as shown in Figure 5-19;

- If the newly added constraints files already exist, Figure 5-20 will pop up when the

user selects "Add to current project". Files cannot be added; however, new blank

files will still be opened in the source files editing area; If "Add to current project" is

not selected, the prompt will not pop up;

- If the newly added Config files already exist, a warning message will be displayed, as per Figure 5-21.

Figure 5-19 Same Name Prompt

SUG100-1.4E 37(83)

Figure 5-20 Constraints Files Existence

Figure 5-21 Config Files Existence

#### 3. Add Project Files

- a) As shown in Figure 5-22, right-click in the blank of the project design area, select "Add Files..." to open the "Select Files" dialog box;

- b). Select single or multiple project files to add.

#### Note!

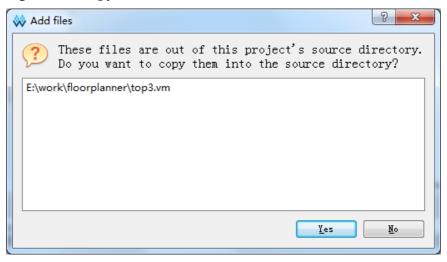

- If the added files are not the project files, Figure 5-23 will pop up to confirm whether the user needs to copy them into the project source directory.

- If the users add RTL files and constraints files at the same time, YunYuan will automatically classify the files in the project design area;

- From the menu bar, click "Project> Add Files..." to add project files.

SUG100-1.4E 38(83)

Figure 5-22 Right-click Actions in Design View

Figure 5-23 Copy File

#### 4. Modify Project Files

Use the following two methods to open and modify the project files, as shown in Figure 5-24:

- a) Double-click any file in the project design area; the file will open in the source file editing area;

- b) Right-click on the name of the file that is to be modified and select "Open".

SUG100-1.4E 39(83)

Figure 5-24 Project Files Editing Actions

#### Note!

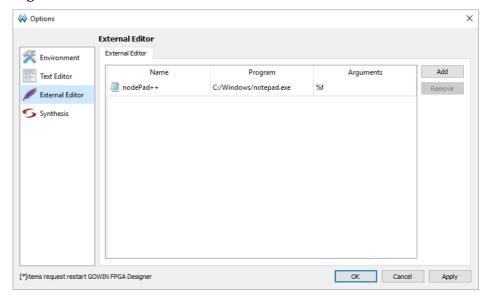

- Users can also select "Open With>Add External Editor" to add an external editor, as shown in Figure 5-25. Users can add external editors according to their needs.

- Users can select"Open Containing Folder"to open the file folder.

- Users can select "Open Terminal Here" to open the command line window. Users can select to run in command line mode.

- If users modify and save a file that has been opened in YunYuan software, the Gowin YunYuan software will generate a change notice, as shown in Figure 5-26.

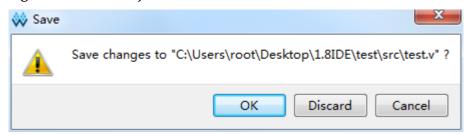

- If users modify and close unsaved files, they will be prompted to save the change as shown in Figure 5-27.

SUG100-1.4E 40(83)

Figure 5-25 External Editor

Figure 5-26 Change Project File

Figure 5-27 Save Project File

#### 5. Delete Project Files

- a) Select the file in the project design area;

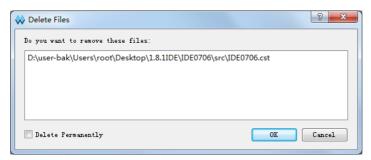

- b) Right-click and select "Remove" or press "Delete" on the keyboard. "Delete Files" will be displayed, as shown in Figure 5-28. If the user selects "Delete Permanently", the file will be deleted from the current project and the disk. If "Delete Permanently" is not selected, the file will only be deleted from the current project.

SUG100-1.4E 41(83)

Figure 5-28 Confirm File Deletion

#### Note!

If the file that is open in the editing area is deleted, the delete file notice will pop up, as shown in Figure 5-29.

Figure 5-29Delete File Notice

## 5.3.3 Modify Project Configuration

- Right-click on the Project Design area;

- 2. Select "Configuration" or select "Project->Configuration..." from the menu bar to open the project configuration view, as shown in Figure 5-30

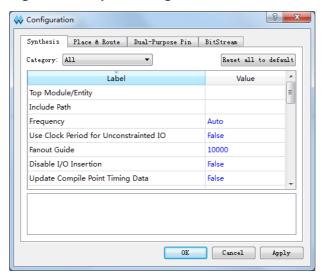

Figure 5-30Project Configuration View

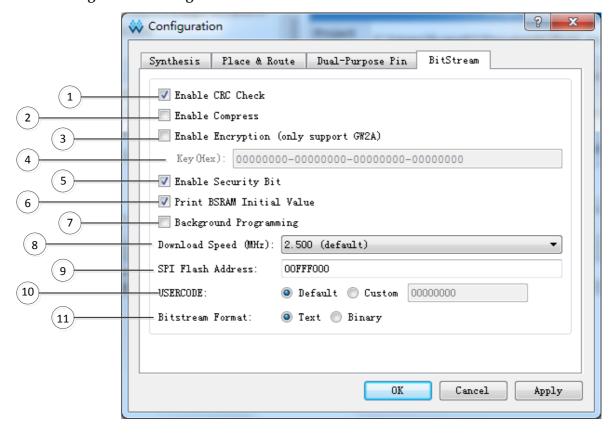

As shown in Figure 5-30, the project configuration contains the Synthesis Configuration, Dual-Purpose Pin Configuration, Place&Route Configuration, Compile Configuration, and Bitstream Configuration tabs:

Synthesis: Used to configure the parameters for optimizing user design with Synplify;

SUG100-1.4E 42(83)

- Place&Route: Used to configure parameters for placing and routing;

- Dual-Purpose Pin: Used to configure duplicated pins;

- Bitstream: Used to configure download speed and enable CRC check, compress, etc.

See the information presented below for further details.

#### 1. Synthesis

- In the configuration view, select Synthesis, and then select the parameters options from the "Category" drop-down list. The default value is "All":

- Select the parameter that needs to be configured in "Lable". The corresponding description shows at the bottom of "Configuration" view;

- Double-click the corresponding value and configure based on your requirements. Click "Apply" to put the current configuration into effect. Click "OK" to complete all the configuration.

#### Note!

- For further details about how to configure common parameters, please refer to Appendix A SynplifyPro Attributes and Directives;

- For further details about the configuration methods, please refer to the Synplifypro manuals in the YunYuan installation directory: installPatj\SynplifyPro\doc;

- For the Post-synthesis, there are no Synthesis options because the design file has been synthesized;

- Reset all to default: Reset all configuration on this page to default values; "Reset" will pop up when you click it, as shown in Figure 5-31.

Figure 5-31 Reset

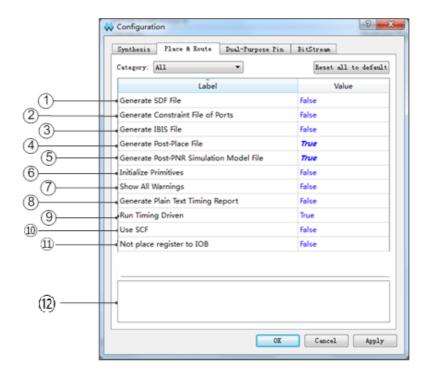

#### 2. Place & Route

Place & Route configuration, which was independently designed by Gowin, is compatible with Gowin YunYuan software. Users can modify the value configuration, as shown in Figure 5-32.

SUG100-1.4E 43(83)

Figure 5-32 Place&Route Configuration

- Generate SDF file

- (3) Generate IBIS Files

- (5) Generate Post-PNR Simulation Model file

- 7 Show all Warnings

- (9) Run Timing Driven

- 11) Not Place Register to IOB

- ② Generate Constraints Files of Ports

- 4) Generate Post-Place file

- (6) Initialize Primitives

- 8 Generate Plain Text Timing Report

- ① Use SCF

- (12) Attributes Description

#### Note!

Reset all to default: Resets all configurations on the page to the default values.

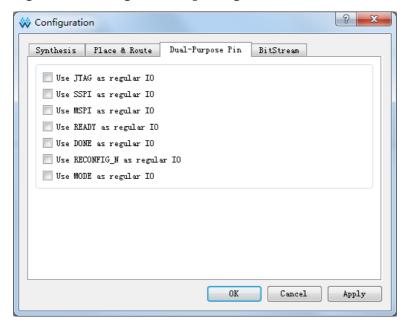

#### 3. Dual-Purpose Pin

In the Dual-Purpose Pin tab, users can configure the multiplexing pins in different modes for the selected device; see Figure 5-33 for the detailed configuration options.

SUG100-1.4E 44(83)

Figure 5-33 Configure Multiplexing Pins

#### Note!

The JTAGSEL\_N and JTAG pins are exclusive. When the JTAG pin is not checked, the JTAGSEL\_N pin will be checked by default. When the JTAG pin is checked, the JTAGSEL\_N pin will not be checked by default.

#### 4. Bitstream

Users can configure the bitstream files format or frequency, etc. See Figure 5-34 for the detailed options.

Figure 5-34 Configure Bitstream File

SUG100-1.4E 45(83)

- 1 Enable a CRC Check

- 3 Enable Encryption (only support GW2A)

- (5) Enable Security Bit

- 7 Remote Upgrade

- 9 SPI Flash Address

- (1) Bitstream Format

- 2 Enable a Compress

- 4 User Defined Key (Hex)

- 6 Print BSRAM Initial Value

- 8 Download Speed (MHz)

- (10) User Code

#### Note!

The SPI Flash address refers to the initial address to which the bitstream will be loaded for the next multiboot. For further details, please refer to <u>Gowin Programmer User Guide</u>.

# 5.4 Manage a Project

The Process view provides a system-level overview of the FGPA design flow, as shown in Figure 5-35. The Process View incorporates the following actions:

- View design summary;

- Start FloorPlanner;

- Start timing constraints editor;

- Implement Synthesis;

- View post Place & Route report;

- Implement Place & Route;

- Check the report generated after Place & Route;

- Start GOWINSEMI FPGA programmer, etc.

SUG100-1.4E 46(83)

Figure 5-35 RTL Project Process Flow

#### Note!

There are no Synthesis (Synplify Pro) options for the post-synthesis because the design file has been synthesized.

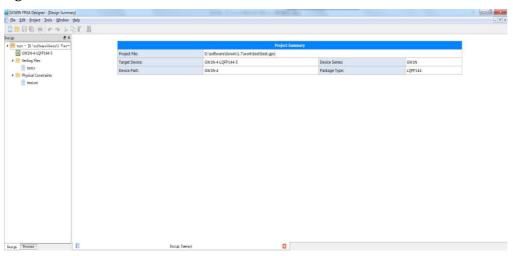

# 5.4.1 Design Summary

When you create an RTL project, YunYuan software will provide a project summary, as shown in Figure 5-36. Use one of the following three methods to open the design summary.

- From the menu bar, select "Window > Design Summary";

- In the Process View, double-click "Design Summary";

- In the Process View, right-click "Design Summary", and then select "Run".

Figure 5-36 Project Summary

| Project Summary |                                                                |                |         |

|-----------------|----------------------------------------------------------------|----------------|---------|

| Project File:   | C:\Users\liyang01\Documents\fpga_project_1\fpga_project_1.gprj |                |         |

| Target Device:  | GW1N-LV4LQ144C5/I4                                             | Device Series: | GW1N    |

| Device Part:    | GW1N-4                                                         | Package Type:  | LQFP144 |

| Core Voltage:   | LV                                                             | Speed Grade:   | C5/I4   |

SUG100-1.4E 47(83)

#### 5.4.2 User Constraints

User constraints provide quick access to and creation of constraints files. For the detailed operation, please refer to the <u>Gowin Design and</u> Constraint User Guide.

User constraint contains the FloorPlanner and Timing Constraints Editor.

Please follow the steps outlined below to use the FloorPlanner:

- Double-click "FloorPlanner" or select "Run" by right-clicking menu. YunYuan software will start the Synthesis and Compile Netlist first, and then open the Physical Constraints Editor.

- 2. If the physical constraints file already exists in the project, the editor will read it directly when the editor is opened.

- 3. If the existing physical constraints file (.cst) is modified and saved, click on the icon in the Physical Constraints Editor to reload the modified constraints file:

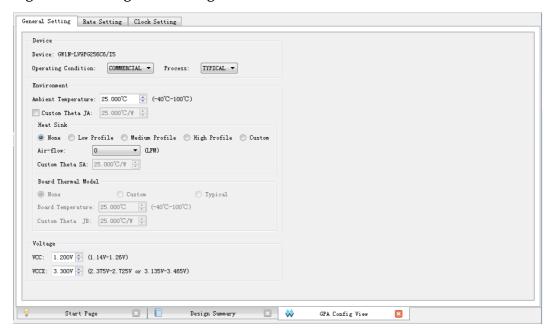

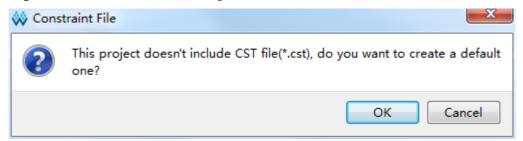

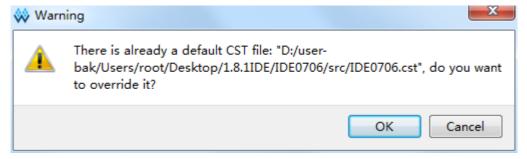

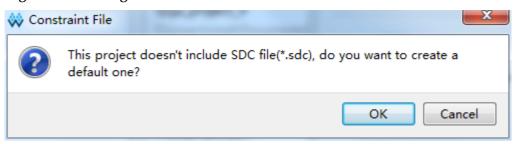

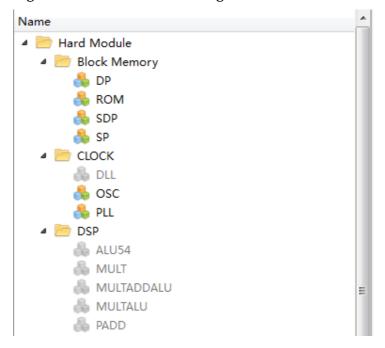

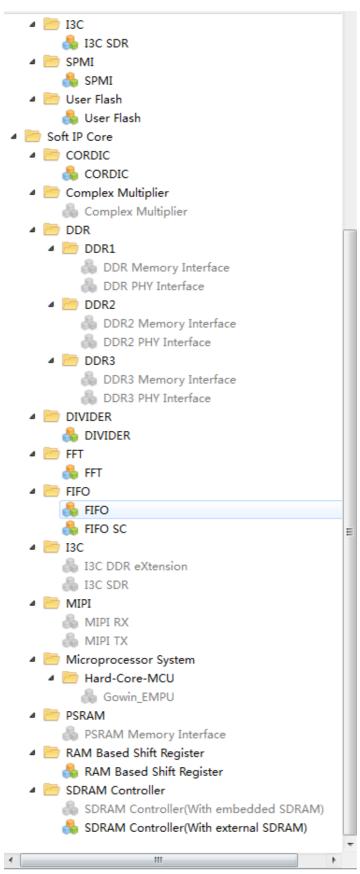

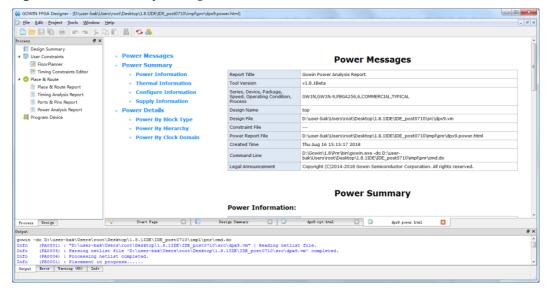

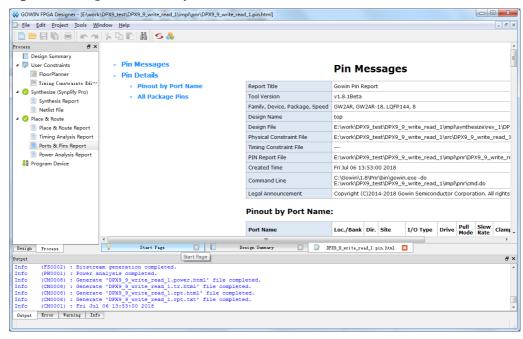

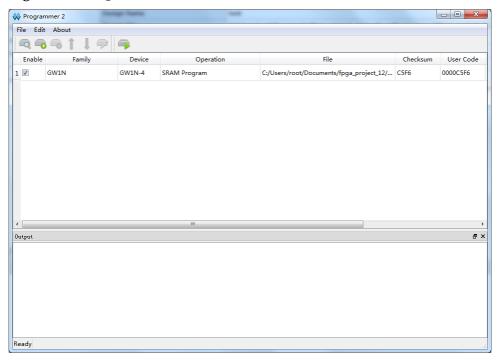

- 4. If the project does not include the physical constraints file, and there is no constraints file in the source file location with the same name, YunYuan will prompt the user to create a constraints file, as shown in Figure 5-37;